Features: • First-ln/First-Out Dual-Port memory

• 64 x 4 organization (IDT72401/03)

• 64 x 5 organization (IDT72402/04)

• IDT72401/02 pin and functionally compatible with

MMI67401/02

• RAM-based FIFO with low falI-through time

• Low-power consumption

- Active: 175mW (typ.)

• Maximum shift rate - 45MHz

• High data output drive capability

• Asynchronous and simultaneous read and write

• Fully expandable by bit width

• Fully expandable by word depth

• IDT72403/04 have Output Enable pin to enable output

data

• High-speed data communications applications

• High-performance CMOS technology

• Available in CERDIP, plastic DIP and SOIC

• Military product compliant to MlL-STD-883, Class B

• Standard Military Drawing #5962-86846 and

5962-89523 is listed on this function.

• Industrial temperature range (40°C to +85°C) is available,

tested to military electrical specificationsPinout Specifications

Specifications

|

Symbol |

Rating |

Com'l & Ind'l |

Commercial |

Unit |

|

VTERM |

Terminal Voltage with

Respect to GND |

0.5 to +70 |

0.5 to +70 |

V |

|

TA |

Operating

Temperature |

0 to +70 |

55 to +125 |

|

|

TBIAS |

Temperature

Under Bias |

55 to +125 |

65 to +135 |

|

|

TSTG |

Storage Temperature |

55 to +125 |

65 to +150 |

|

|

IOUT |

DC Output Current |

50 |

50 |

mA |

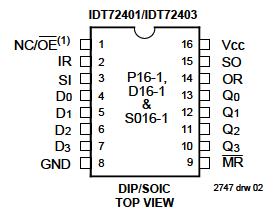

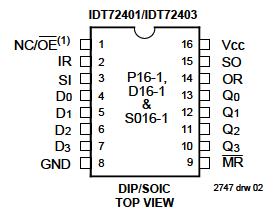

DescriptionThe IDT72401 and IDT72403 are asynchronous highperformance First-ln/First-Out memories organized 64 words by 4 bits. The IDT72402 and IDT72404 are asynchronous high-performance First-ln/First-Out memories organized as 64 words by 5 bits. The IDT72403 and IDT72404 also have an Output Enable (OE ) pin. The FlFOs accept 4-bit or 5-bit data at the data input (D0-D3, 4). The stored data stack up on a firstin/ first-out basis.

A Shift Out (SO) signal of the IDT72403 causes the data at the next to last word to be shifted to the output while all other data shifts down one location in the stack. The Input Ready (IR) signal acts like a flag to indicate when the input is ready for new data (IR = HIGH) or to signal when the FIFO is full (IR = LOW). The Input Ready signal can also be used to cascade multiple devices together. The Output Ready (OR) signal is a flag to indicate that the output remains valid data (OR = HIGH) or to indicate that the FIFO is empty (OR = LOW). The Output Ready can also be used to cascade multiple devices together.

Width expansion of the IDT72403 is accomplished by logically ANDing the Input Ready (IR) and Output Ready (OR) signals to form composite signals.

Depth expansion of the IDT72403 is accomplished by tying the data inputs of one device to the data outputs of the previous device. The Input Ready pin of the receiving device is connected to the Shift Out pin of the sending device and the Output Ready pin of the sending device is connected to the Shift In pin of the receiving device.

Reading and writing operations of the IDT72403 are completely asynchronous allowing the FIFO to be used as a buffer between two digital machines of widely varying operating frequencies. The 45MHz speed makes these FlFOs ideal for high-speed communication and controller applications.

Military grade product of the IDT72403 is manufactured in compliance with the latest revision of MIL-STD-883, Class B.

IDT72403 Data Sheet

IDT72403 Data Sheet