Features: · 128K x 36 memory configuration, flow-through outputs

· Supports high performance system speed - 95 MHz(8ns Clock-to-Data Access)

· ZBTTM Feature - No dead cycles between write and read ycles

· Internally synchronized signal eliminates the need to ontrol OE

· Single R/W (READ/WRITE) control pin

· 4-word burst capability (Interleaved or linear)

· Individual byte write (BW1 - BW4) control (May tie active)

· Three chip enables for simple depth expansion

· Single 3.3V power supply (±5%)

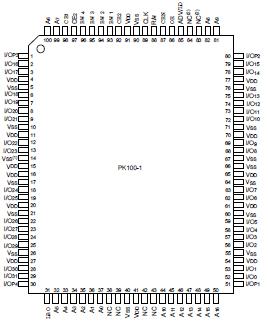

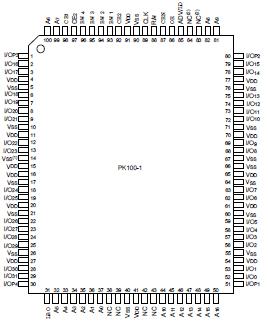

· Packaged in a JEDEC standard 100-pin TQFP packagePinout Specifications

Specifications

| Symbol |

Rating |

Commercial

& Industrial

|

Unit |

| VTERM(2) |

Terminal Voltage with Respect to GND |

-0.5 to +4.6 |

V |

| VTERM(3) |

Terminal Voltage with Respect to GND |

0.5 to VDD+0.5 |

V |

| TA |

Operating Temperature |

0 to +70 |

|

| TBIAS |

Temperature Under Bias |

55 to +125 |

|

| TSTG |

Storage Temperature |

55 to +125 |

|

| PT |

Power Dissipation |

2.0 |

W |

| IOUT |

DC Output Current |

50 |

mA |

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VDD and Input terminals only.

3. I/O terminals.DescriptionThe IDT71V547 is a 3.3V high-speed 4,718,592-bit (4.5 Megabit) ynchronous SRAM organized as 128K x 36 bits. It is designed to eliminate ead bus cycles when turning the bus around between reads and writes, r writes and reads. Thus it has been given the name ZBTTM, or Zero Bus urn-around.

Address and control signals are applied to the SRAM during one clock ycle, and on the next clock cycle, its associated data cycle occurs, be it ead or write.

The IDT71V547 contains address, data-in and control signal registers. he outputs are flow-through (no output data register). Output enable is he only asynchronous signal and can be used to disable the outputs at ny given time.

A Clock Enable (CEN) pin allows operation of the IDT71V547 to e suspended as long as necessary. All synchronous inputs are gnored when CEN is high and the internal device registers will hold heir previous values.

There are three chip enable pins (CE1, CE2, CE2) that allow the user o deselect the device when desired. If any one of these three is not active hen ADV/LD is low, no new memory operation can be initiated and any urst in progress is stopped. However, any pending data transfers (reads r writes) will be completed. The data bus will tri-state one cycle after the hip was deselected or write initiated.

he IDT71V547 has an on-chip burst counter. In the burst mode, the DT71V547 can provide four cycles of data for a single address presented o the SRAM. The order of the burst sequence is defined by the LBO input in. The LBO pin selects between linear and interleaved burst sequence. he ADV/LD signal is used to load a new external address (ADV/LD = OW) or increment the internal burst counter (ADV/LD = HIGH).

The IDT71V547 SRAM utilizes IDT's high-performance, high-volume .3V CMOS process, and is packaged in a JEDEC Standard 14mm x 0mm 100-pin thin plastic quad flatpack (TQFP) for high board density.

IDT71V547 Data Sheet

IDT71V547 Data Sheet