Features: • High-speed address to MATCH comparison time

- Commercial: 8/10/12/15/20ns (max.)

• High-speed address access time

- Commercial: 8/10/12/15/20ns (max.)

• High-speed chip select access time

- Commercial: 6/7/8/10ns (max.)

• Power-ON Reset Capability

• Low power consumption

- 830mW (typ.) for 12ns parts

- 880mW (typ.) for 10ns parts

- 920mW (typ.) for 8ns parts

• Produced with advanced BiCMOS high-performance

technology

• Input and output directly TTL-compatible

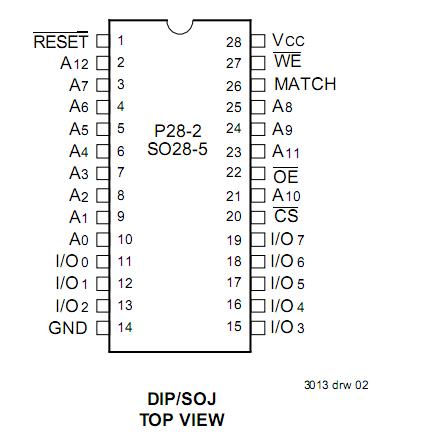

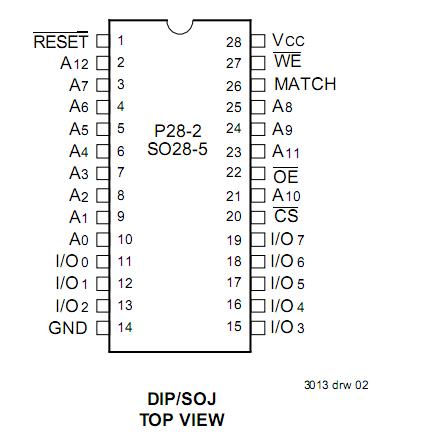

• Standard 28-pin plastic DIP and 28-pin SOJ (300 mil)Pinout Specifications

Specifications

|

Symbol |

Rating |

Com'l. |

Unit |

|

VTERM(2)

|

Terminal Voltage wi

Respect to GND |

0.5 to +0.7 |

V |

|

TA

|

Operating Temperature |

0 to +70 |

°C |

|

TBIAS |

Temperature Under Bias |

55 to +125 |

°C |

|

TSTG |

Storage Temperature |

55 to +125 |

°C |

|

PT |

Power Dissipation |

1.0 |

W |

|

IOUT |

DC Output Current |

50 |

mA |

NOTES: 3013 tbl 03

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VTERM must not exceed VCC + 0.5V.DescriptionThe IDT71B74 is a high-speed cache address comparator subsystem consisting of a 65,536-bit static RAM organized as 8K x 8 and an 8-bit comparator. A single IDT71B74 can map 8K cache words into a 2 megabyte address space by using the 21 bits of address organized with the 13 LSBs for the cache address bits and the 8 higher bits for cache data bits. Two IDT71B74s can be combined to provide 29 bits of address

comparison, etc. The IDT71B74 also provides a single RAM clear control, which clears all words in the internal RAM to zero when activated. This allows the tag bits for all locations to be cleared at power-on or system-reset, a requirement for cache comparator systems. The IDT71B74 can also be used as a resettable 8K x 8 high-speed static RAM.

The IDT71B74 is fabricated using IDT's high-performance, high-reliability BiCMOS technology. Address access times as fast as 8ns, chip select times of 6ns and address-to-match times of 8ns are available.

The MATCH pin of several IDT71B74s can be wired-ORed together to provide enabling or acknowledging signals to the data cache or processor, thus eliminating logic delays and increasing system throughput.

IDT71B74 Data Sheet

IDT71B74 Data Sheet