Features: •Single 3.3±0.3V power supply

•All device pins are compatible with LVTTL interface

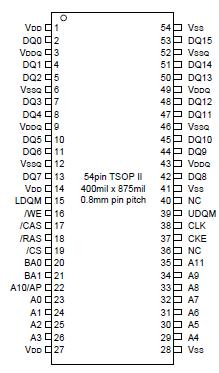

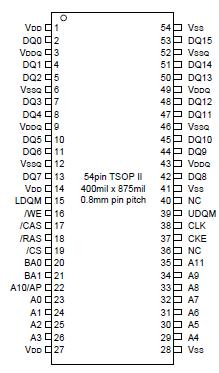

•JEDEC standard 400mil 54pin TSOP-II with 0.8mm of pin pitch

•All inputs and outputs referenced to positive edge of system clock

•Data mask function by UDQM or LDQM

•Internal four banks operation

•Auto refresh and self refresh

•4096 refresh cycles / 64ms

•Programmable Burst Length and Burst Type - 1, 2, 4, 8 or Full page for Sequential Burst - 1, 2, 4 or 8 for Interleave Burst

•Programmable CAS Latency ; 2, 3 Clocks

Pinout Specifications

Specifications

|

MAXIMUM RATINGS |

Symbol |

Rating |

Unit |

| Ambient Temperature |

TA |

0 ~ 70 |

°C |

| Storage Temperature |

TSTG |

-55 ~ 125 |

°C |

| Voltage on Any Pin relative to VSS |

VIN, VOUT |

-1.0 ~ 4.6 |

V |

| Voltage on VDD relative to VSS |

VDD, VDDQ |

-1.0 ~ 4.6 |

V |

| Short Circuit Output Current |

IOS |

50 |

mA |

| Power Dissipation |

PD |

1 |

W |

| Soldering Temperature ⋅ Time |

TSOLDER |

260 ⋅ 10 |

°C · Sec |

DescriptionThe Hynix HY57V281620HC(L/S)T is a 134,217,728bit CMOS Synchronous DRAM, ideally suited for the main memory applications which require large memory density and high bandwidth. It is organized as 4banks of 2,097,152x16

HY57V281620HC(L/S)T is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.

HY57V281620HC(L/S)T Programmable options include the length of pipeline (Read latency of 2 or 3), the number of consecutive read or write cycles initiated by a single control command (Burst length of 1,2,4,8, or full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipelined design is not restricted by a `2N` rule.)

HY57V281620HC(L/S)T Data Sheet

HY57V281620HC(L/S)T Data Sheet