Features: Generates/detects digital bit patterns foranalyzing, evaluating and troubleshootingdigital communications systems

Operates at speeds from DC to 20 MHz

Programmable polynomial length andfeedback taps for generation of any otherpseudorandom pattern up to

32bitsin lengthincluding: 26-1, 29-1, 211-1, 215-1, 220-1, 223-1,and 232-1

Programmable user-defined pattern andlength for generation of any repetitive patternup to 32 bits in length

Large 32-bit error count and bit countregisters

Software programmable bit error insertion

Fully independent transmit and receivesections

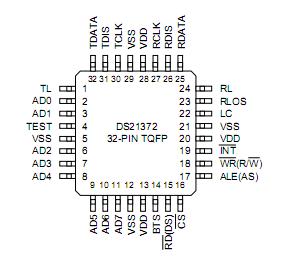

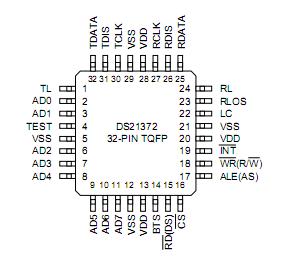

8-bit parallel control port

Detects test patterns with bit error rates up to10-2Pinout SpecificationsVoltage on Any Pin Relative to Ground ...........-1.0V to +7.0V

SpecificationsVoltage on Any Pin Relative to Ground ...........-1.0V to +7.0V

Operating Temperature for DS21372TN...........-40 to +85

Storage Temperature ................................... -55 to +125

Soldering Temperature ................................ See J-STD-020ADescriptionThe DS21372 Bit Error Rate Tester (BERT) is a software programmable test pattern generator, receiver,and analyzer capable of meeting the most stringent error performance requirements of digitaltransmission facilities. Two categories of test pattern generation (Pseudo-random and Repetitive)conform to CCITT/ITU O.151, O.152, O.153, and O.161 standards. The DS21372 operates at clock ratesranging from DC to 20 MHz. This wide range of operating frequency allows the DS21372 to be used inexisting and future test equipment, transmission facilities, switching equipment, multiplexers, DACs,Routers, Bridges, CSUs, DSUs, and CPE equipment.

The DS21372 user-programmable pattern registers provide the unique ability to generate loopbackpatterns required for T1, Fractional-T1, Smart Jack, and other test procedures. Hence the DS21372 caninitiate the loopback, run the test, check for errors, and finally deactivate the loopback.The DS21372 consists of four functional blocks: the pattern generator, pattern detector, error counter, andcontrol interface. The DS21372 can be programmed to generate any pseudorandom pattern with length upto 232-1 bits (see Table 5, Note 9) or any user programmable bit pattern from 1 to 32 bits in length. Logicinputs can be used to configure the DS21372 for applications requiring gap clocking such as Fractional-T1, Switched-56, DDS, normal framing requirements, and per-channel test procedures. In addition, theDS21372 can insert single or 10-1to 10-7bit errors to verify equipment operation and connectivity.

DS21372 Data Sheet

DS21372 Data Sheet