Mounting Type: Surface Mount

Series: -

Operating Temperature: 0°C ~ 70°C

Packaging: Tube

Manufacturer: National Semiconductor

Voltage - Supply: 4.75 V ~ 5.25 V

Current - Supply: 140mA

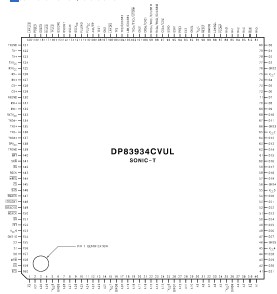

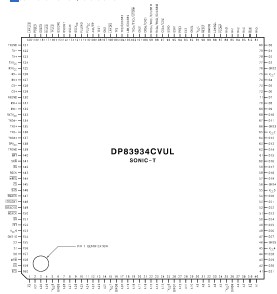

Package / Case: 160-BQFP

Supplier Device Package: 160-PQFP (28x28)

Controller Type: Network Interface Controller (NIC)

Interface: Twisted Pair

Features: 32-bit non-multiplexed address and data bus

Auto AUI/TPI selection

High-speed interruptible DMA

Linked-list buffer management maximizes flexibility

Two independent 32-byte transmit and receive FIFOs

Bus compatibility for all standard microprocessors

Supports big and little endian formats

Integrated IEEE 802.3 ENDEC

Integrated Twisted Pair Interface

Complete address filtering for up to 16 physical and/or multicast addresses

32-bit general-purpose timer

Loopback diagnostics

Fabricated in low-power CMOS

160 PQFP package

Full network management facilities support the 802.3 layer management standard

Integrated support for bridge and repeater applicationsPinout SpecificationsSupply Voltage (VCC) ........................................0.5V to 7.0V

SpecificationsSupply Voltage (VCC) ........................................0.5V to 7.0V

DC Input Voltage (VIN) ...........................0.5V to VCC a 0.5V

DC Output Voltage (VOUT) ......................0.5V to VCC a 0.5V

Storage Temperature Range (TSTG) ................65 to 150

Power Dissipation (PD) 500 mW

Lead Temp. (TL) (Soldering, 10 sec.) ............................260

ESD Rating

(RZAP e 1.5k, CZAP e 120 pF) .....................................1.5 kVDescriptionThe SONIC-T (Systems-Oriented Network Interface Controller with Twisted Pair) is a second-generation Ethernet Controller designed to meet the demands of today's high-speed 32- and 16-bit systems. Its system interface operates with a high speed DMA that typically consumes less than 5% of the bus bandwidth. Selectable bus modes provide both big and little endian byte ordering and a clean interface to standard microprocessors. The linked-list buffer management system of DP83934CVUL-20 offers maximum flexibility in a variety of environments from PC-oriented adapters to high-speed motherboard designs. Furthermore, the DP83934CVUL-20 integrates a fully-compatible IEEE 802.3 Encoder/Decoder (ENDEC) and a Twisted Pair Interface which provide a one-chip solution for Ethernet when using 10BASE-T. When using 10BASE2 or 10BASE5, the SONIC-T may be paired with the DP8392 Coaxial Transceiver Interface to achieve a simple 2-chip solution.

For increased performance, the DP83934CVUL-20 implements a unique buffer management scheme to efficiently process receive and transmit packets in system memory. No intermediate packet copy is necessary. The DP83934CVUL-20 buffer management uses three areas in memory for (1) allocating additionaldescriptors to the memory resource area. The transmit buffer management uses two areas in memory: 1. indicating status and control information; 2. fetching packet data. The system can create a transmit queue allowing multiple packets to be transmitted from a single transmit command. The packet data can reside on any arbitrary byte boundary and can exist in several non-contiguous locations. resources, (2) indicating status information, and (3) buffering packet data. During reception, the DP83934CVUL-20 stores packets in the buffer area, then indicates receive status and control information in the descriptor area. The system allocates more memory resources to the DP83934CVUL-20 by adding

Parameters: | Technical/Catalog Information | DP83934CVUL-20 |

| Vendor | National Semiconductor |

| Category | Integrated Circuits (ICs) |

| Controller Type | Network Interface Controller |

| Interface | Twisted Pair |

| Voltage - Supply | 4.75 V ~ 5.25 V |

| Current - Supply | 140mA |

| Package / Case | 132-PQFP |

| Packaging | Tube |

| Operating Temperature | 0°C ~ 70°C |

| Lead Free Status | Contains Lead |

| RoHS Status | RoHS Non-Compliant |

| Other Names | DP83934CVUL 20

DP83934CVUL20

|

DP83934CVUL-20 Data Sheet

DP83934CVUL-20 Data Sheet