Features: • Low-power 3.3V, 0.18m CMOS technology

• Low power consumption < 270mW Typical

• 3.3V MAC Interface

• Auto-MDIX for 10/100 Mb/s

• Energy Detection Mode

• 25 MHz clock out

• SNI Interface (configurable)

• RMII Rev. 1.2 Interface (configurable)

• MII Serial Management Interface (MDC and MDIO)

• IEEE 802.3u MII

• IEEE 802.3u Auto-Negotiation and Parallel Detection

• IEEE 802.3u ENDEC, 10BASE-T transceivers and filters

• IEEE 802.3u PCS, 100BASE-TX transceivers and filters

• IEEE 1149.1 JTAG

• Integrated ANSI X3.263 compliant TP-PMD physical sublayer with adaptive equalization and Baseline Wander compensation

• Programmable LED support Link, 10 /100 Mb/s Mode, Activity, and Collision Detect

• Single register access for complete PHY status

• 10/100 Mb/s packet BIST (Built in Self Test)

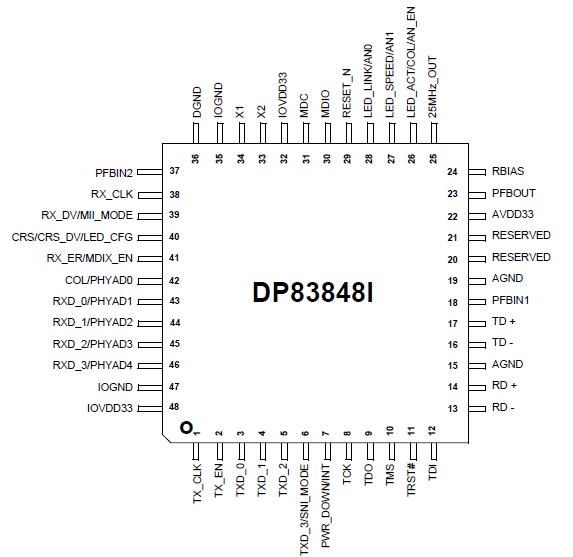

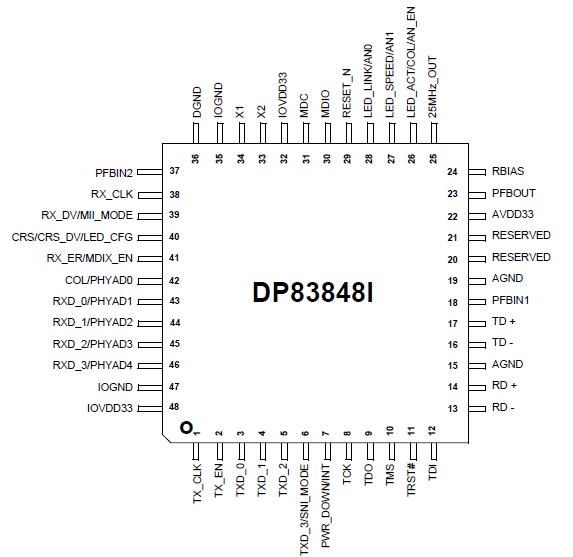

• 48-pin LQFP package (7mm) x (7mm)Application• High End Peripheral Devices

• Industrial Controls and Factory Automation

• General Embedded ApplicationsPinout Specifications

Specifications

| Temperature Min |

-40 deg C |

| Temperature Max |

85 deg C |

| Supply Voltage |

3.3 Volt |

| View Using Catalog |

Supply Voltage (VCC)-0.5 V to 4.2 V

DC Input Voltage (VIN) -0.5V to VCC + 0.5V

DC Output Voltage (VOUT) -0.5V to VCC + 0.5V

Storage Temperature (TSTG)-65oC to 150°C

Max case temp for TA = 85°C 107 °C

Max. die temperature (Tj) 150 °C

Lead Temp. (TL)

(Soldering, 10 sec.) 260 °C

ESD Rating

(RZAP = 1.5k, CZAP = 120 pF) 4.0 kV

DescriptionThe DP83848I is a robust fully featured 10/100 single port Physical Layer device offering low power consumption, including several intelligent power down states. These low power modes increase overall product reliability due to decreased power dissipation. Supporting multiple intelligent power modes allows the application to use the absolute minimum amount of power needed for operation. In addition to low power, the DP83848I is optimized for cable length performance far exceeding IEEE specifications.

The DP83848I includes a 25MHz clock out. This means that the application can be designed with a minimum of external parts, which in turn results in the lowest possible total cost of the solution. The DP83848I easily interfaces to twisted pair media via an external transformer and fully supports JTAG IEEE specification 1149.1 for ease of manufacturing. Additionally both MII and RMII are supported ensuring ease and flexibility of design.

The DP83848I features integrated sublayers to support both 10BASE-T and 100BASE-TX Ethernet protocols, which ensures compatibility and interoperability with all other standards based Ethernet solutions. The DP83848I is offered in a small form factor (48 pin LQFP) so that a minimum of board space is needed.

DP83848I Data Sheet

DP83848I Data Sheet