Series: -

Voltage - Supply: 4.5 V ~ 5.5 V

Packaging: Tube

Operating Temperature: 0°C ~ 70°C

Memory Size: 256K (32K x 8)

Format - Memory: RAM

Interface: Parallel

Memory Type: SRAM - Asynchronous

Speed: 35ns

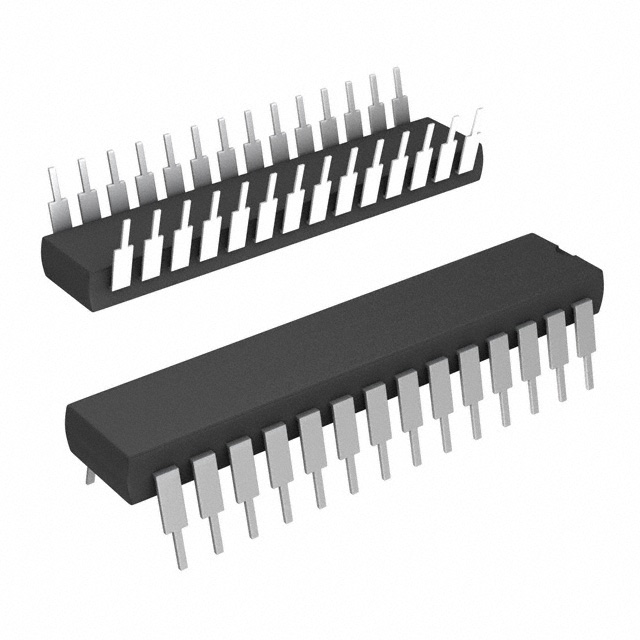

Supplier Device Package: 28-PDIP

Manufacturer: Cypress Semiconductor Corp

Package / Case: 28-DIP (0.300", 7.62mm)

Features: • High speed

-10 ns

• Fast tDOE

• CMOS for optimum speed/power

• Low active power

-467 mW (max, 12 ns "L" version)

• Low standby power

-0.275 mW (max, "L" version)

• 2V data retention ("L" version only)

• Easy memory expansion with CE and OE features

• TTL-compatible inputs and outputs

• Automatic power-down when deselectedPinout Specifications(Above which the useful life may be impaired. For user guidelines,

Specifications(Above which the useful life may be impaired. For user guidelines,

not tested.)

Storage Temperature .................................65°C to +150°C

Ambient Temperature with

Power Applied.............................................55°C to +125°C

Supply Voltage to Ground Potential

(Pin 28 to Pin 14) .......................................... 0.5V to +7.0V

DC Voltage Applied to Outputs

in High-Z State[1] ..................................0.5V to VCC + 0.5V

DC Input Voltage[1]...............................0.5V to VCC + 0.5V

Output Current into Outputs (LOW)............................ 20 mA

Static Discharge Voltage.......................................... > 2001V

(per MIL-STD-883, Method 3015)

Latch-up Current.................................................... > 200 mADescriptionThe CY7C199 is a high-performance CMOS static RAM organized as 32,768 words by 8 bits. Easy memory expansion is provided by an active LOW Chip Enable (CE) and active LOW Output Enable (OE) and three-state drivers. This device has an automatic power-down feature, reducing the power consumption by 81% when deselected. The CY7C199 is in the standard 300-mil-wide DIP, SOJ, and LCC packages.

An active LOW Write Enable signal (WE) of CY7C199 controls the writing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O0 through I/O7) is written into the memory location addressed by the address present on the address pins (A0 through A14). Reading the device is accomplished by selecting theCY7C199 and enabling the outputs, CE and OE active LOW, while WE remains inactive or HIGH. Under these conditions, the contents of the location addressed by the information on address pins are present on the eight data input/output pins.

The input/output pins of CY7C199 remain in a high-impedance state unless the chip is selected, outputs are enabled, and Write Enable (WE) is HIGH. A die coat is used to improve alpha immunity.

CY7C199-35PC Data Sheet

CY7C199-35PC Data Sheet