Features: •High speed

-15 ns

•Fast tDOE

•Low active power

-715 mW

•Low standby power

-220 mW

•CMOS for optimum speed/power

•Easy memory expansion with CE</a>1, CE</a>2, and OE</a> features

•TTL-compatible inputs and outputs

•Automatic power-down when deselectedPinout Specifications(Above which the useful life may be impaired. For user guide-lines, not tested.)

Specifications(Above which the useful life may be impaired. For user guide-lines, not tested.)

Storage Temperature .............................65°C to +150°C

Ambient Temperature with

Power Applied.........................................55°C to +125°C

Supply Voltage to Ground Potential...............0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State[3]..........................................0.5V to +7.0V

DC Input Voltage[3].......................................0.5V to +7.0V

Output Current into Outputs (LOW).............................20 mA

Static Discharge Voltage........................................... >2001V

(per MIL-STD-883, Method 3015)

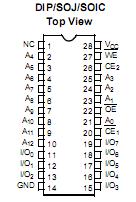

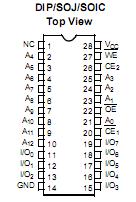

Latch-Up Current.................................................... >200 mADescriptionThe CY7C185 is a high-performance CMOS static RAM orga-nized as 8192 words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE</a>1), an active HIGHchip enable (CE</a>2), and active LOW output enable (OE</a>) and three-state drivers. This device has an automatic power-down

feature (CE</a>1 or CE</a>2), reducing the power consumption by 70% when deselected. The CY7C185 is in a standard 300-mil-wide DIP, SOJ, or SOIC package.

An active LOW write enable signal (WE</a>) controls the writ-ing/reading operation of the memory. When CE</a>1 and WE</a> in- puts are both LOW and CE</a>2 is HIGH, data on the eight data input/output pins (I/O0 through I/O7) is written into the memory location addressed by the address present on the address pins (A0 through A12). Reading the CY7C185 is accomplished by selecting theCY7C185 and enabling the outputs, CE</a>1 and OE</a> active LOW, CE</a>2 active HIGH, while WE</a> remains inactive or HIGH. Under these conditions, the contents of the location ad- dressed by the information on address pins are present on the eight data input/output pins.

The input/output pins of CY7C185 remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE</a>) is HIGH. A die coat is used to insure alpha immunity.

CY7C185 Data Sheet

CY7C185 Data Sheet