Features: • Fast access times: 7.5, 8.5, 10.0 ns

• Fast clock speed: 117, 100, 83 MHz

• Provide high-performance 3-1-1-1 access rate

• Optimal for depth expansion

• 3.3V (5% / +10%) power supply

• Common data inputs and data outputs

• Byte Write Enable and Global Write control

• Chip enable for address pipeline

• Address, data and control registers

• Internally self-timed Write Cycle

• Burst control pins (interleaved or linear burst sequence)

• Automatic power down available using ZZ mode or CE deselect

• High-density, high-speed packages

• JTAG boundary scan for BGA packaging versionPinout Specifications(Above which the useful life may be impaired. For user guidelines,

Specifications(Above which the useful life may be impaired. For user guidelines,

not tested.)

Storage Temperature ..................................... −55°C to +150°C

Ambient Temperature with

Power Applied.................................................. −55°C to +125°C

Supply Voltage on VDD Relative to GND.........−0.5V to +4.6V

DC Voltage Applied to Outputs

in High Z State[9])................................ −0.5V to VDDQ + 0.5V

DC Input Voltage[9]..................................−0.5V to VDDQ + 0.5V

Current into Outputs (LOW) .........................................20 mA

Static Discharge Voltage .......................................... >1500V

(per MIL-STD-883, Method 3015)

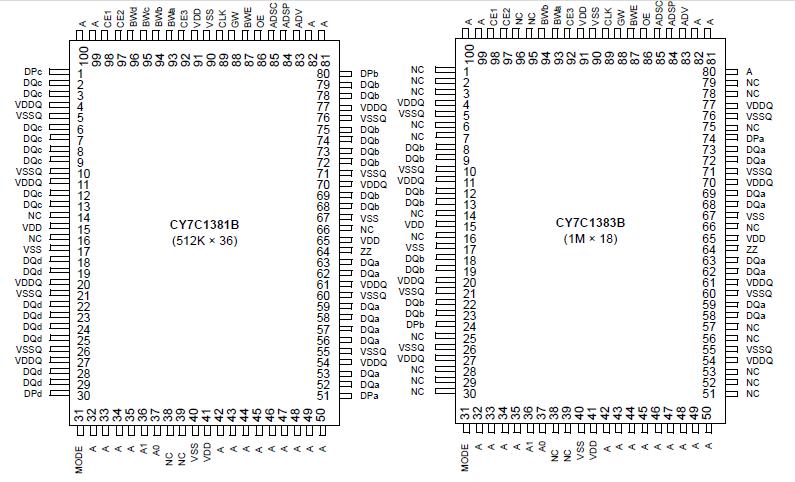

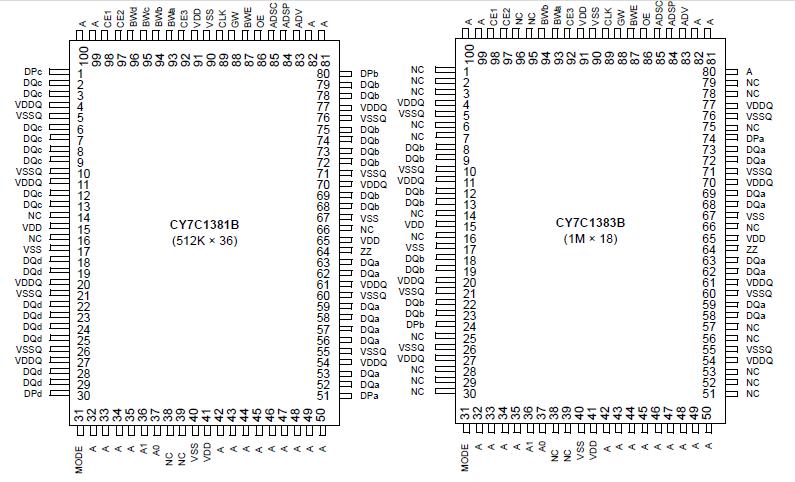

Latch-Up Current.................................................... >200 mADescriptionThe Cypress Synchronous Burst SRAM CY7C1381B and CY7C1383B family employs high-speed, low power CMOS designs using advanced single-layer polysilicon, triple-layer metal technology. Each memory cell consists of six transistors. The CY7C1381B and CY7C1383B SRAMs integrate 524,288 × 36 and 1,048,576 × 18 SRAM cells with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation. All synchronous inputs are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs of CY7C1381B and CY7C1383B include all addresses, all data inputs, address-pipelining Chip Enable (CE), Burst Control Inputs (ADSC, ADSP, and ADV), Write Enables (BWa, BWb, BWc, BWd, and BWe), and Global Write (GW).

Asynchronous inputs of CY7C1381B and CY7C1383B include the Output Enable (OE) and Burst Mode Control (MODE). The data outputs (Q), enabled by OE, are also asynchronous.

Addresses and chip CY7C1381B and CY7C1383B enables are registered with either Address Status Processor (ADSP) or address status controller (ADSC) input pins. Subsequent burst addresses can be internally generated as controlled by the Burst Advance Pin (ADV).

Address, data inputs, and Write controls CY7C1381B and CY7C1383B are registered on-chip to initiate self-timed Write cycle. Write cycles can be one to four bytes wide as controlled by the Write control inputs. Individual byte Write allows individual byte to be written. BWa controls DQ1-DQ8 and DP1. BWb controls DQ9-DQ16 and DP2. BWc controls DQ17-DQ24and DP3. BWd controls DQ25-DQ32 and DP4. BWa, BWb BWc, and BWd of CY7C1381B and CY7C1383B can be active only with BWe being LOW. GW being LOW causes all bytes to be written. Write pass-through capability allows written data available at the output for the immediately next Read cycle. CY7C1381B and CY7C1383B also incorporates pipelined enable circuit for easy depth expansion without penalizing system performance.

All inputs and outputs of the CY7C1381B and the CY7C1383B are JEDEC-standard JESD8-5-compatible.

CY7C1381B Data Sheet

CY7C1381B Data Sheet