Features: •No Bus Latency (NoBL) architecture eliminates dead cycles between write and read cycles

•Can support up to 133-MHz bus operations with zero wait states Data is transferred on every clock

•Pin-compatible and functionally equivalent to ZBT™ devices

•Internally self-timed output buffer control to eliminate the need to use OE

•Registered inputs for flow-through operation

•Byte Write capability

•3.3V/2.5V I/O power supply

•Fast clock-to-output times 6.5 ns (for 133-MHz device) 8.5 ns (for 100-MHz device)

•Clock Enable (CEN) pin to enable clock and suspend operation

•Synchronous self-timed writes

•Asynchronous Output Enable

•Offered in JEDEC-standard lead-free 100 TQFP, 119-ball BGA and 165-ball fBGA packages

•Three chip enables for simple depth expansion

•Automatic Power-down feature available using ZZ mode or CE deselect

•JTAG boundary scan for BGA and fBGA packages

•Burst Capability-linear or interleaved burst order

•Low standby power

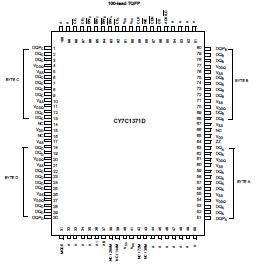

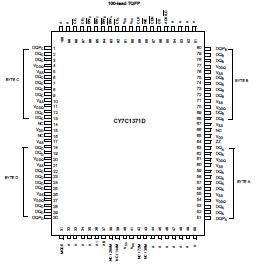

Pinout Specifications

Specifications(Above which the useful life may be impaired. For user guidelines,

not tested.)

Storage Temperature ..............................................................65°C to +150°C

Ambient Temperature with

Power Applied...........................................................................55°C to +125°C

Supply Voltage on VDD Relative to GND.......................................... 0.5V to +4.6V

DC Voltage Applied to Outputs

in Tri-State........................................... ................................0.5V to VDDQ + 0.5V

DC Input Voltage.....................................................................0.5V to VDD + 0.5V

Current into Outputs (LOW)............................................................................20 mA

Static Discharge Voltage..............................................................................> 2001V

(per MIL-STD-883, Method 3015)

Latch-up Current........................................................................................ > 200 mA

DescriptionThe CY7C1371D/CY7C1373D is a 3.3V, 512K x 36/1 Mbit x 18 Synchronous Flow-through Burst SRAM designed specifically to support unlimited true back-to-back Read/Write operations without the insertion of wait states. The CY7C1371D/ CY7C1373D is equipped with the advanced No Bus Latency (NoBL) logic required to enable consecutive Read/Write operations with data being transferred on every clock cycle. This feature dramatically improves the throughput of data through the SRAM, especially in systems that require frequent

Write-Read transitions.

All synchronous inputs of CY7C1371D/CY7C1373D pass through input registers controlled by the rising edge of the clock. The clock input is qualified by the Clock Enable (CEN) signal, which when deasserted suspends operation and extends the previous clock cycle. Maximum access CY7C1371D/CY7C1373D delay from the clock rise is 6.5 ns (133-MHz device).

Write operations of CY7C1371D/CY7C1373D are controlled by the two or four Byte Write Select (BWX) and a Write Enable (WE) input. All writes are conducted with on-chip synchronous self-timed write circuitry.

Three synchronous Chip Enables (CE1, CE2, CE3) and an asynchronous Output Enable (OE)CY7C1371D/CY7C1373D provide for easy bank selection and output tri-state control. In order to avoid bus contention, the output drivers are synchronously tri-stated during the data portion of a write sequence.

CY7C1371D Data Sheet

CY7C1371D Data Sheet