Features: • FCT-E speed at 3.8 ns

• Power-off disable outputs permits live insertion

• Edge-rate control circuitry for significantly improved noise characteristics

• Typical output skew < 250 ps

• ESD > 2000V

• TSSOP (19.6 mil pitch) and SSOP (25-mil pitch) packages

• Industrial temperature range of -40°C to +85°C

• VCC = 5V ± 10%

CY74FCT16501T Features:

• 64 mA sink current, 32 mA source current

• Typical VOLP (ground bounce) <1.0V at VCC = 5V, TA = 25°C

CY74FCT162501T Features:

• Balanced 24 mA output drivers

• Reduced system switching noise

• Typical VOLP (ground bounce) <0.6V at VCC = 5V, TA= 25°C

CY74FCT162H501T Features:

• Bus hold retains last active state

• Eliminates the need for external pull-up or pull-down resistorsPinout SpecificationsStorage Temperature ............................................................-55°C to +125°C

SpecificationsStorage Temperature ............................................................-55°C to +125°C

Ambient Temperature with Power Applied..............................-55°C to +125°C

DC Input Voltage.......................................................................... -0.5V to +7.0V

DC Output Voltage........................................................................ -0.5V to +7.0V

DC Output Current (Maximum Sink Current/Pin).......................... -60 to +120 mA

Power Dissipation........................................................................................ 1.0W

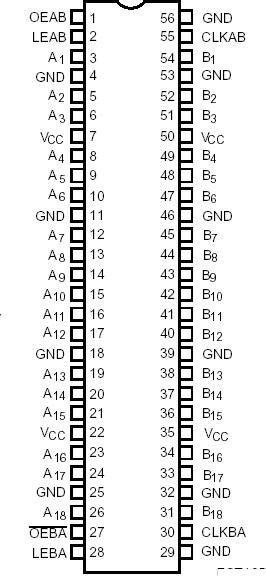

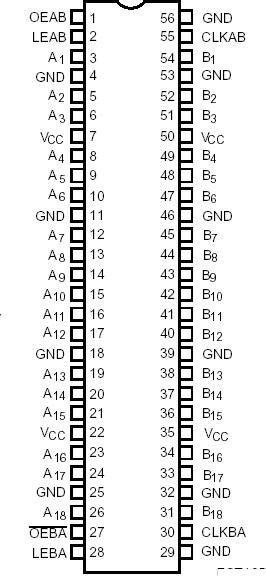

Static Discharge Voltage ......................................................................... >2001VDescriptionThese 18-bit universal bus transceivers of CY74FCT162501T can be operated in transparent, latched or clock modes by combining D-type latches and D-type flip-flops. Data flow in each direction is controlled by output enable (OEAB and OEBA ), latch enable (LEAB and LEAB ), and clock inputs (CLKAB and CLKAB). For A-to-B data flow, the CY74FCT162501T operates in transparent mode when LEAB is HIGH. When LEAB is LOW, the A data is latched if CLKAB is held at a HIGH or LOWlogic level. If LEAB is LOW, the A bus data is stored in the latch/flip-flop on the LOW-to-HIGH transition of CLKAB. OEAB performs the output enable function on the B port. Data flow from B-to-A is similar to that of A-to-B and is controlled by OEBA , LEBA, and CLKAB.

The output buffers of CY74FCT162501T are designed with a power-off disable feature to allow live insertion of boards.

The CY74FCT16501T is ideally suited for driving high-capacitance loads and low-impedance backplanes.

THE CY74FCT162501T has 24-mA balanced output drivers with current limiting resistors in the outputs. This reduces the need for external terminating resistors and provides for minimal undershoot and reduced ground bounce. The CY74FCT162501T is ideal for driving transmission lines.

The CY74FCT162H501T is a 24-mA balanced output part, that has "bus hold" on the data inputs. The device retains the input's last state whenever the input goes to high impedance. This eliminates the need for pull-up/down resistors and prevents floating inputs.

CY74FCT162501T Data Sheet

CY74FCT162501T Data Sheet