Features: • Low voltage range:

-CY62136V: 2.7V-3.6V

• Ultra-low active, standby power

• Easy memory expansion with CE and OE features

• TTL-compatible inputs and outputs

• Automatic power-down when deselected

• CMOS for optimum speed/powerPinout SpecificationsStorage Temperature ................................65°C to +150°C

SpecificationsStorage Temperature ................................65°C to +150°C

Ambient Temperature with

Power Applied............................................55°C to +125°C

Supply Voltage to Ground Potential................ 0.5V to +4.6V

in High Z State[1].................................... 0.5V to VCC + 0.5V

DC Input Voltage[1].................................0.5V to VCC + 0.5V

Output Current into Outputs (LOW)..............................20 mA

Static Discharge Voltage............................................>2001V

(per MIL-STD-883, Method 3015)

Latch-Up Current.....................................................>200 mADescriptionThe CY62136V is a high-performance CMOS static RAM organized as 131,072 words by 16 bits. This device features advanced circuit design to provide ultra-low active current. This is ideal for providing More Battery Life™ (MoBL™) in portable applications such as cellular telephones. The device also has an automatic power-down feature that significantly reduces power consumption by 99% when addresses are not toggling.

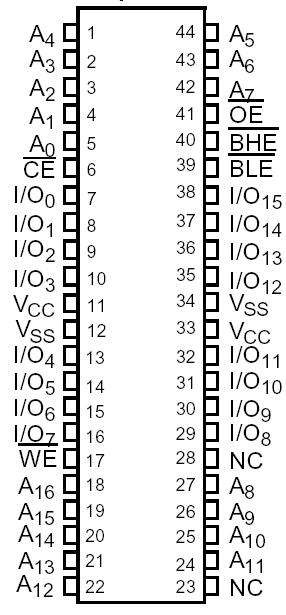

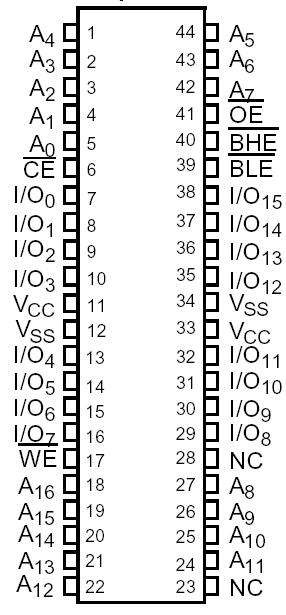

The device can also be put into standby mode when deselected (CE HIGH). The input/output pins (I/O0 through I/O15) are placed in a high-impedance state when: deselected (HIGH), outputs are disabled (OE HIGH), outputs are disabled (OE HIGH), BHE and BLE are disabled (BHE, BLE HIGH), or during a write operation (CE LOW, and WE LOW).

Writing to the CY62136V is accomplished by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte Low Enable (BLE ) is LOW, then data from I/O pins (I/O0 through I/O7), is written into the location specified on the address pins (A0 through A16). If Byte High Enable (BHE) is LOW, then data from I/O pins (I/O8 through I/O15) is written into the location specified on the address pins (A0 through A16).

Reading from the device is accomplished by taking Chip Enable (CE ) and Output Enable (OE ) LOW while forcing the Write Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW, then data from the memory location specified by the address pins will appear on I/O0 to I/O7. If Byte High Enable (BHE) is LOW,then data from memory will appear on I/O8 to I/O15. See the Truth Table at the back of this data sheet for a complete description of read and write modes.

The CY62136V is available in 48-ball FBGA and standard 44-pin TSOP Type II (forward pinout) packaging.

CY62136V Data Sheet

CY62136V Data Sheet