Features: • High-accuracy PLL with 12-bit multiplier and 10-bit divider

• EPROM-programmability

• 3.3V or 5V operation

• Operating frequency

-390 kHz133 MHz at 5V

-390 kHz100 MHz at 3.3V

• Reference input from either a 1030 MHz fundamental toned crystal or a 175 MHz external clock

• EPROM-selectable TTL or CMOS duty-cycle levels

• Sixteen selectable post-divide options, using either PLL or reference oscillator/external clock

• Programmable PWR_DWN or OE pin, with asynchronous or synchronous modes

• Low jitter outputs typically

-80 ps at 3.3V/5V

• Controlled rise and fall times and output slew rate

• Available in both commercial and industrial temperature ranges

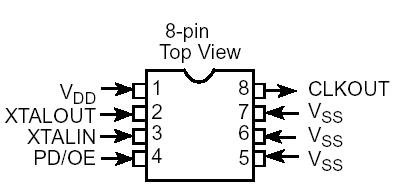

• Factory-programmable device optionsPinout SpecificationsSupply Voltage ..................................................0.5 to +7.0V

SpecificationsSupply Voltage ..................................................0.5 to +7.0V

Input Voltage........................................... 0.5V to VDD +0.5V

Storage Temperature (Non-Condensing).... 55°C to +150°C

Junction Temperature................................................. 150°C

Static Discharge Voltage.......................................... 2000V

DescriptionThe CY2077 is an EPROM-programmable, high-accuracy,general-purpose, PLL-based design for use in applications such as modems, disk drives, CD-ROM drives, video CD players, DVD players, games, set-top boxes, and data/telecommunications.

The CY2077 can generate a clock output up to 133 MHz at 5V or 100 MHz at 3.3V. It has been designed to give the customer a very accurate and stable clock frequency with little to zero PPM error. The CY2077 contains a 12-bit feedback counter divider and 10-bit reference counter divider to obtain a very high resolution to meet the needs of stringent design specifications.

Furthermore, there are eight output divide options of/1, /2, /4, /8, /16, /32, /64, and /128. The output divider can select between the PLL and crystal oscillator output/external clock, providing a total of 16 different options to add more flexibility in designs. TTL or CMOS duty cycles can be selected. Power management with the CY2077 is also very flexible. The user may choose either a PWR_DWN or an OE feature with which both have integrated pull-up resistors. PWR_DWN and OE signals can be programmed to have asynchronous and synchronous timing with respect to the output signal. There is a weak pull-down on the output that will pull CLKOUT LOW when either the PWR_DWN or OE signal is active. This weak pull-down can easily be overridden by another clock signal in designs where multiple clock signals share a signal path.

Multiple options for output selection, better power distribution layout, and controlled rise and fall times enable the CY2077 to be used in applications that require low jitter and accurate reference frequencies.

CY2077 Data Sheet

CY2077 Data Sheet