Features: ·Fully differential signal path

·Non-Blocking

·Flexible expansion to larger array sizes with very low power

·Single +5/−5V or dual ±5V operation

·TRI-STATE outputs

·Double row latch architecture

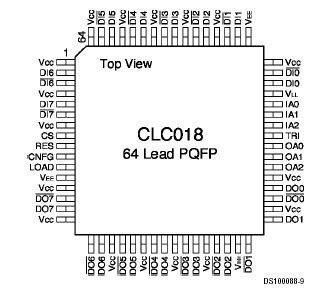

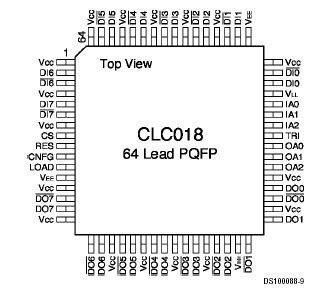

·64-lead PQFP packageApplication·Serial digital video routing (SMPTE 259M)

·Telecom/datacom switching

·ATM SONETPinout SpecificationsSupply Voltage (VCCVEE) −0.3V to +6.0V

SpecificationsSupply Voltage (VCCVEE) −0.3V to +6.0V

VLL Maximum VCC +6V

VLL Minimum VCC −0.5V

Storage Temperature Range −65 to +150

Lead Temp. (Soldering 4 sec.) +260

ESD Rating TBD

Package Thermal Resistance

JA 64-Pin PQFP 75/W

JC 64-Pin PQFP 15/W

Reliability Information

Transistor Count 3000

MTTF (based on limited life test data) TBDDescriptionNational's Comlinear CLC018 is a fully differential 8x8 digital crosspoint switch capable of operating at data rates exceeding 1.4 Gbps per channel. Its non-blocking architecture utilizes eight independent 8:1 multiplexers to allow each output to be independently connected to any input and any input to be connected to any or all outputs. Additionally, each output can be individually disabled and set to a high-impedance state. This TRI-STATE® feature allows flexible expansion to larger switch array sizes.

Low channel-to-channel crosstalk allows the CLC018 to provide superior all-hostile jitter of 50 psPP. This excellent signal fidelity along with low power consumption of 850 mW make the CLC018 ideal for digital video switching plus a variety of data communication and telecommunication applications.

The fully differential signal path provides excellent noise immunity, and the I/Os support ECL and PECL logic levels. In addition, the inputs may be driven single-ended or differentially and accept a wide range of common mode levels including the positive supply. Single +5V or -5V supplies or dual +5V supplies are supported. CLC018 Dual supply mode allows the control signals to be referenced to the positive supply (+5V) while the high-speed I/O remains ECL compatible.

The double row latch architecture utilized in the CLC018 allows switch reprogramming to occur in the background during operation. Activation of the new configuration occurs with a single "configure" pulse. Data integrity and jitter performance on unchanged outputs are maintained during reconfiguration. Two reset modes are provided. Broadcast reset results in all outputs being connected to input port DI0. TRI-STATE Reset results in all outputs being disabled.

The CLC018 is fabricated on a high-performance BiCMOS process and is available in a 64-lead plastic quad flat pack (PQFP).

CLC018 Data Sheet

CLC018 Data Sheet