Features: • SPI (Serial Peripheral Interface)

• Full Clock Features

- Seconds, Minutes, Hours (12/24, AM/PM), Day of Week, Date, Month, Year (0-99), Automatic Leap Year

• 32 Word x 8-Bit RAM

• Seconds, Minutes, Hours Alarm

• Automatic Power Loss Detection

• Low Minimum Standby (Timekeeping) Voltage. . . 2.2V

• Selectable Crystal or 50/60Hz Line Input

• Buffered Clock Output

• Battery Input Pin that Powers Oscillator and also Connects to VDD Pin When Power Fails

• Three Independent Interrupt Modes

- Alarm

- Periodic

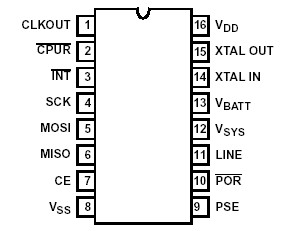

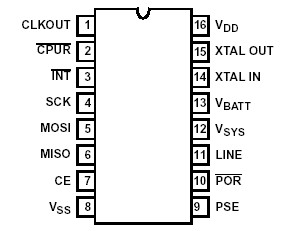

- Power-Down SensePinout SpecificationsSupply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7V

SpecificationsSupply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7V

Input Voltage, VIN . . . . . . . . . . . . . . . . . . VSS -0.3V to VDD +0.3V

Current Drain Per Input Pin Excluding VDD and VSS, I . . . . . .10mA

Current Drain Per Output Pin, I. . . . . . . . . . . . . . . . . . . . . . .40mADescriptionThe CDP68HC68T1 Real-Time Clock provides a time/calendar function, a 32 byte static RAM, and a 3 wire Serial Peripheral Interface (SPI Bus). The primary function of the clock is to divide down a frequency input that can be supplied by the on-board oscillator in conjunction with an external crystal or by an external clock source. CDP68HC68T1 internal oscillator can operate with a 32kHz, 1MHz, 2MHz, or 4MHz crystal. An external clock source with a 32kHz, 1MHz, 2MHz, 4MHz, 50Hz or 60Hz frequency can be used to drive the CDP68HC68T1. The time registers hold seconds, minutes, and hours, while the calendar registers hold day-of-week, date, month, and year information. The data is stored in BCD format. In addition, 12 or 24 hour operation can be selected. In 12 hour mode, an AM/PM indicator is provided. The T1 has a programmable output which can provide one of seven outputs for use elsewhere in the system. Computer handshaking is controlled with a wired-OR interrupt output. The interrupt can be programmed to provide a signal as the result of: An alarm programmed to occur at a predetermined combination of seconds, minutes, and hours. One of 15 periodic interrupts ranging from sub-second to once per day frequency. A power fail detect. The CDP68HC68T1 PSE output and the VSYS input are used for external power control. The CPUR output is available to reset the processor under power-down conditions. CPUR is enabled under software control and can also be activated via the CDP68HC68T1s watchdog. If enabled, the watchdog requires a periodic toggle of the CE pin without a serial transfer.

CDP68HC68T1 Data Sheet

CDP68HC68T1 Data Sheet