Features: • High Voltage Type (20V Rating)

• Medium Speed Operation 10MHz (typ.) at VDD - VSS = 10V

• Fully Static Operation

• 100% Tested for Quiescent Current at 20V

• Standardized Symmetrical Output Characteristics

• 5V, 10V and 15V Parametric Ratings

• Maximum Input Current of 1a at 18V Over Full Package- Temperature Range;

100nA at 18V and 25oC

• Noise Margin (Over Full Package Temperature Range):

1V at VDD = 5V

2V at VDD = 10V

2.5V at VDD = 15V

• Meets All Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

Application• Fixed and Programmable Divided- By-10, 9, 8, 7, 6, 5, 4, 3, 2 Counters

• Fixed and Programmable Counters Greater Than 10

• Programmable Decade Counters

• Divide-By- "N" Counters/Frequency Synthesizers

• Frequency Division

• Counter Control/Timers

Pinout SpecificationsDC Supply Voltage Range, (VDD)..0.5V to +20V (Voltage Referenced to VSS Terminals)

SpecificationsDC Supply Voltage Range, (VDD)..0.5V to +20V (Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs .....................................................-0.5V to VDD +0.5V

DC Input Current, Any One Input.......................................................................±10mA

Operating Temperature Range ................. -55 to +125 Package Types D, F, K, H

Storage Temperature Range (TSTG).................................................. -65 to +150

Lead Temperature (During Soldering) ............................................................. +265

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for 10s MaximumDescriptionCD4018BMS types consist of 5 Johnson-Counter stages, buffered Q outputs from each stage, and counter preset control gating. CLOCK, RESET, DATA, PRESET ENABLE, and 5 individual JAM inputs are provided. Divide by 10, 8, 6, 4, or 2 counter configurations can be implemented by feeding theQ5, Q4, Q3, Q2,Q1 signals, respectively, back to the DATA input. Divide-by-9, 7, 5, or 3 counter configurations can be implemented by the use of a CD4011B to gate the feedback connection to the DATA input. Divide by functions greater than 10 can be achieved by use of multiple CD4018BMS units. The counter is advanced one count at the positive clock-signal transition. Schmitt Trigger action on the clock line permits unlimited clock rise and fall times. A high RESET signal clears the counter to an all-zero condition. A high PRESET-ENABLE signal allows information on the JAM inputs to preset the counter. Anti-lock gating is provided to assure the proper counting sequence.

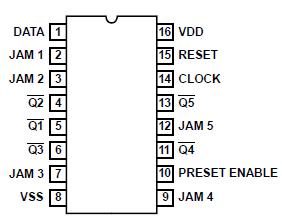

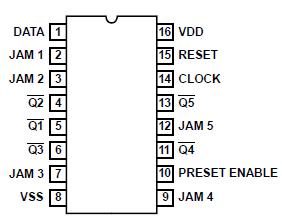

The CD4018BMS is supplied in these 16-lead outline packages:

Braze Seal DIP H4T

Frit Seal DIP H1F

Ceramic Flatpack H6W

CD4018BMS Data Sheet

CD4018BMS Data Sheet