Features: Fastest data rate of any Am8530

- 8.192 MHz / 2.048 Mb/s

- 10 MHz / 2.5 Mb/s

- 16.384 MHz / 4.096 Mb/s

Low-power CMOS technology

Pin and function compatible with other NMOS and CMOS 8530s

Easily interfaced with most CPUs

- Compatible with non-multiplexed bus

Many enhancements over NMOS Am8530H

- Allows Am85C30 to be used more effectively in high-speed applications

- Improves interface capabilities

Two independent full-duplex serial channels

Asynchronous mode features

- Programmable stop bits, clock factor, character length and parity

- Break detection/generation

- Error detection for framing, overrun, and parity

Synchronous mode features

- Supports IBMâ BISYNC, SDLC, SDLC Loop, HDLC, and ADCCP Protocols

- Programmable CRC generators and checkers

- SDLC/HDLC support includes frame control, zero insertion and deletion, abort, and residue handling

Enhanced SCC functions support high-speed frame reception using DMA

- 14-bit byte counter

- 10 ´ 19 SDLC/HDLC Frame Status FIFO

- Independent Control on both channels

- Enhanced operation does not allow special receive conditions to lock the 3-byte DATA FIFO when the 10 ´ 19 FIFO is enabled

Local Loopback and Auto Echo modes

Internal or external character synchronization

2-Mb/s FM encoding transmit and receive capability using internal DPLL for 16.384-MHz product

Internal synchronization between RxC to PCLK and TxC to PCLK

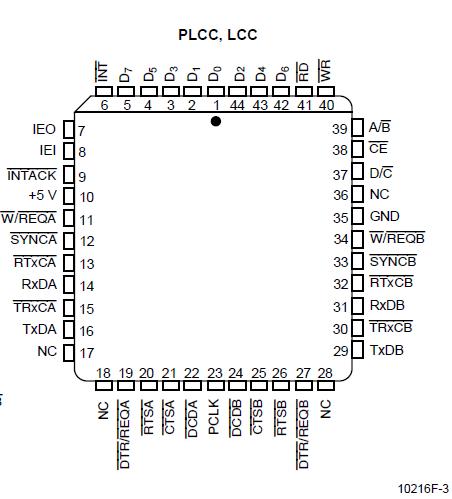

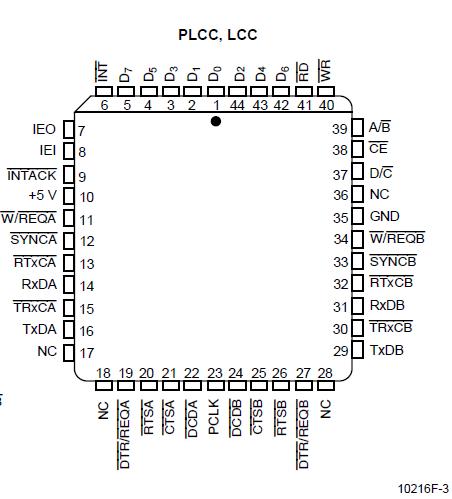

- This allows the user to eliminate external synchronization hardware required by the NMOS device when transmitting or receiving data at the maximum rate of 1/4 PCLK frequencyPinout

SpecificationsStorage Temperature . . . . . . . . . . . 65 to +150

SpecificationsStorage Temperature . . . . . . . . . . . 65 to +150

Voltage at any Pin

Relative to VSS . . . . . . . . . . . . . . . 0.5 to +7.0 V

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality

at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device

reliabilityDescriptionAMD's Am85C30 is an enhanced pin-compatible version of the popular Am8530H Serial Communications Controller. The Enhanced Serial Communications Controller (ESCC) is a high-speed, low-power, multiprotocol communications peripheral designed for use with 8- and 16-bit microprocessors. It has two independent, full-duplex channels and functions as a serial-toparallel, parallel-to-serial converter/controller. AMD's proprietary enhancements make the Am85C30 easier to interface and more effective in high-speed applications due to a reduction in software burden and the elimination of the need for some external glue logic.

The Am85C30 is easy to use due to a variety of sophisticated internal functions, including on-chip baud rate generators, digital phase-locked loops, and crystal oscillators, which dramatically reduce the need for external logic. The device can generate and check CRC codes in any SYNC mode, and can be programmed to check data integrity in various modes. The ESCC also has facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

This versatile Am85C30 supports virtually any serial data transfer application such as networks, modems, cassettes, and tape drivers. The ESCC is designed for nonmultiplexed buses and is easily interfaced with most CPUs, such as 80188, 80186, 80286, 8080, Z80, 6800, 68000 and MULTIBUS

tm

Am85C30 Data Sheet

Am85C30 Data Sheet