Features:

Single power supply operation

-5.0 V ± 10% for read, erase, and program operations

-Simplifies system-level power requirements

Manufactured on 0.32 µm process technology

-Compatible with Am29F010 and Am29F010A device

High performance

-45 ns maximum access time

Low power consumption

-12 mA typical active read current

-30 mA typical program/erase current

-<1 µA typical standby current

Flexible sector architecture

-Eight 16 Kbyte sectors

-Any combination of sectors can be erased

-Supports full chip erase

Sector protection

-Hardware-based feature that disables/re-

enables program and erase operations in any

combination of sectors

-Sector protection/unprotection can be implemented using standard PROM programming equipment

Embedded Algorithms

-Embedded Erase algorithm automatically pre-programs and erases the chip or any combination of designated sector

-Embedded Program algorithm automatically programs and verifies data at specified address

Erase Suspend/Resume

-Supports reading data from a sector not being erased

Minimum 1 million erase cycles guaranteed per sector

20-year data retention at 125°C

-Reliable operation for the life of the system

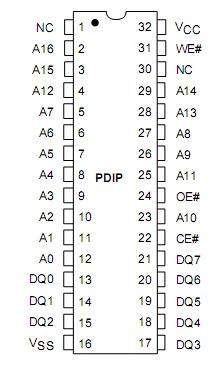

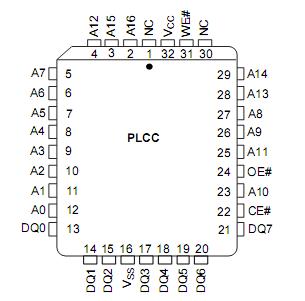

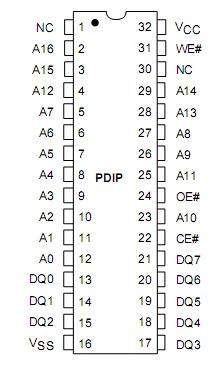

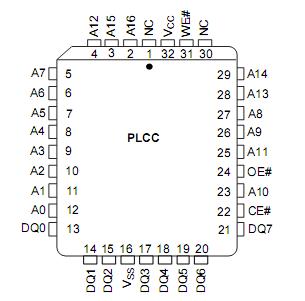

Package options

-32-pin PLCC

-32-pin TSOP

-32-pin PDIP

Compatible with JEDEC standards

-Pinout and software compatible with single-power-supply flash

-Superior inadvertent write protection

Data# Polling and Toggle Bits

-Provides a software method of detecting program or erase cycle completion

Pinout

SpecificationsStorage Temperature

SpecificationsStorage Temperature

Plastic Packages . . . . . . . . . . . . . . .65°C to +125°C

Ambient Temperature

with Power Applied . . . . . . . . . . . . .55°C to +125°C

Voltage with Respect to Ground

VCC (Note 1). . . . . . . . . . . . . . . . . . . .2.0 V to +7.0 V

A9 (Note 2). . . . . . . . . . . . . . . . .. . . .2.0 V to +13.0 V

All other pins (Note 1) . . . . . . . . . . .. .2.0 V to +7.0 V

Output Short Circuit Current (Note 3) . . .... . . . 200 mADescriptionThe Am29F010B is a 1 Mbit, 5.0 Volt-only Flash emory organized as 131,072 bytes. The Am29F010B isoffered in 32-pin PDIP, PLCC and TSOP packages. The byte-wide data appears on DQ0-DQ7. The de-vice is designed to be programmed in-system with the tandard system 5.0 Volt VCC supply. A 12.0 volt V PP is notrequired for program or erase operations. The device canalso be programmed or erased in standard EPROMprogrammers.

Am29F010B is manufactured using AMD's 0.32 µm pro-cess technology, and offers all the features and benefits f the Am29F010 and Am29F010A. The standard device offers access times of 45, 55, 70,90, and 120 ns, allowing high-speed microprocessorsto operate without wait states. To eliminate bus conten-tion the device has separate chip enable (CE#), writeenable (WE#) and output enable (OE#) controls.The device requires only a single 5.0 volt power sup-ply for both read and write functions. Internallygenerated and regulated voltages are provided for theprogram and erase operations.

Am29F010B is entirely command set compatible with theJEDEC single-power-supply Flash standard. Com-mands are written to the command register usingstandard microprocessor write timings. Register con-tents serve as input to an internal state machine thatcontrols the erase and programming circuitry. Write cycles also internally latch addresses and data neededfor the programming and erase operations. Reading dta out of Am29F010B is similar to reading from otherFlash or EPROM devices.Device programming occurs by executing the programcommand sequence. This invokes the EmbeddedProgram algorithm-an internal algorithm that auto-matically times the program pulse widths and verifiesproper cell margin.

Device erasure occurs by executing the erase com-mand sequence. This invokes the Embedded Erasealgorithm-an internal algorithm that automatically pre-programs the array (if it is not already programmed)before executing the erase operation. During erase,the device automatically times the erase pulse widths and verifies proper cell margin.

The host system can detect whether a program orerase operation is complete by reading the DQ7 (Data#Polling) and DQ6 (toggle) status bits. After a programor erase cycle has been completed, the device is readyto read array data or accept another command. The sector erase architectureallows memory sectorsto be erased and reprogrammed without affecting thedata contents of other sectors. Am29F010B is erasedwhen shipped from the factory.The hardware data protection measures include alow VCC detector automatically inhibits write operationsduring power transitions. The hardware sector protec-tion feature disables both program and eraseoperations in any combination of the sectors of memory,and is implemented using standard EPROMprogrammers.

The system can place the device into the standby mode.Power consumption is greatly reduced in this mode.AMD's Flash technology combines years of Flash memory manufacturing experience to produce thehighest levels of quality, reliability, and costeffectiveness. Am29F010B electrically erases all bits within a sector simultaneously via Fowler-Nordheimtunneling. The bytes are programmed one byte at atime using the EPROM programming mechanism of hot electron injection.

Am29F010B Data Sheet

Am29F010B Data Sheet