High-density, High-performance, Electrically-erasable Complex

Programmable Logic Device

3.0 to 3.6V Operating Range

64 Macrocells

5 Product Terms per Macrocell, Expandable up to 40 per Macrocell

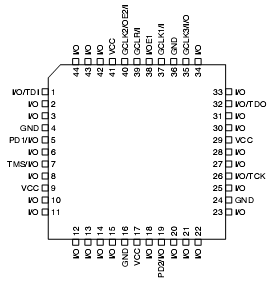

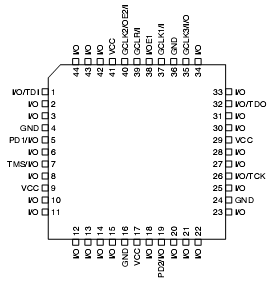

44, 68, 84, 100 Pins

15 ns Maximum Pin-to-pin Delay

Registered Operation up to 77 MHz

Enhanced Routing Resources

In-System Programmability (ISP) via JTAG

Flexible Logic Macrocell

D/T/Latch Configurable Flip-flops

Global and Individual Register Control Signals

Global and Individual Output Enable

Programmable Output Slew Rate

Programmable Output Open-collector Option

Maximum Logic Utilization by Burying a Register with a COM Output

Advanced Power Management Features

Automatic 5 A Standby for "L" Version

Pin-controlled 100 A Standby Mode (Typical)

Programmable Pin-keeper Circuits on Inputs and I/Os

Reduced-power Feature per Macrocell

Available in Commercial and Industrial Temperature Ranges

Available in 44-, 68-, and 84-lead PLCC; 44- and 100-lead TQFP; and 100-lead PQF

Advanced EE Technology

100% Tested

Completely Reprogrammable

10,000 Program/Erase Cycles

20 Year Data Retention

2000V ESD Protection

200 mA Latch-up Immunity

JTAG Boundary-scan Testing to IEEE Std. 1149.1-1990 and 1149.1a-1993 Supporte

PCI-compliant

Security Fuse Feature

Pinout

Specifications

Temperature Under Bias.................................. -40 to +85

Storage Temperature..................................... -65 to +150

Voltage on Any Pin with

Respect to Ground .........................................-2.0V to +7.0V(1)

Voltage on Input Pins

with Respect to Ground

During Programming.....................................-2.0V to +14.0V(1)

Programming Voltage with

Respect to Ground .......................................-2.0V to +14.0V(1)

Description

The ATF1504ASV(L) is a high-performance, high-density complex programmable logic device (CPLD) that utilizes Atmel's proven electrically-erasable memory technology.With 64 logic macrocells and up to 68 inputs, it easily integrates logic from several TTL,SSI, MSI, LSI and classic PLDs.

The ATF1504ASV(L)'s enhanced routing switch matri-es increase usable gate count and the odds of successful pin-locked design modifications.The ATF1504ASV(L) has up to 68 bi-directional I/O pins and four dedicated input pins,depending on the type of device package selected. Each dedicated pin can also serve as a global control signal, register clock, register reset or output enable. Each of these ontrol signals can be selected for use individually within each macrocell. Each of the 64 macrocells generates a buried feedback that goes to the global bus.Each input and I/O pin also feeds into the global bus. The switch matrix in each logic block then selects 40 individual signals from the global bus. Each macrocell also gener-ates a foldback logic term that goes to a regional bus. Cascade logic between macrocells in the ATF1504ASV(L) allows fast, efficient generation of complex logic func-ions.

The ATF1504ASV(L) contains four such logic chains, each capable of creating um term logic with a fan-in of up to 40 product terms.The ATF1504ASV (L) macrocell, shown in Figure 1, is flexible enough to support highly-omplex logic functions operating at high speed. The macrocell consists of five sections:product terms and product term select multiplexer, OR/XOR/CASCADE logic, a flip-flop,output select and enable, and logic array inputs.

ATF1504ASV Data Sheet

ATF1504ASV Data Sheet