Features: `Input frequency range: 20MHz - 50MHz.

`Zero input - output propagation delay.

`Low-skew outputs.

-Output-output skew less than 250pS.

-Device-device skew less than 700pS.

`Less than 200pS cycle-to-cycle jitter is compatible with Pentium® based systems.

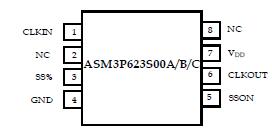

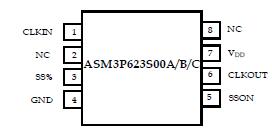

`Available in 16pin, 150mil SOIC, 4.4mm TSSOP (ASM3P623S00D/E/F), and in 8pin, 150 mil SOIC,4.4mm TSSOP Packages (ASM3P623S00A/B/C).

`3.3V operation

`Advanced 0.35 CMOS technology.

`The First True Drop-in Solution.

Pinout Specifications

Specifications

|

Parameter |

Min |

Max |

Unit |

| Supply Voltage to Ground Potential |

-0.5 |

+7.0 |

V |

| DC Input Voltage (Except CLKIN) |

-0.5 |

VDD + 0.5 |

V |

| DC Input Voltage (CLKIN) |

-0.5 |

7 |

V |

| Storage Temperature |

-65 |

+150 |

°C |

| Max. Soldering Temperature (10 sec) |

|

260 |

°C |

| Junction Temperature |

|

150 |

°C |

Static Discharge Voltage

(As per JEDEC STD22- A114-B) |

|

2000 |

V |

Note: These are stress ratings only and functional usage is not implied. Exposure to absolute maximum ratings for prolonged periods can affect device reliability.DescriptionASM3P623S00D/E/F is a versatile, 3.3V zero-delay buffer designed to distribute high-speed clocks. It accepts one reference input and drives out eight low-skew clocks. It is available in a 16pin package. The ASM3P623S00A/B/C is the eight-pin version of the ASM3P623S00. It accepts one reference input and drives out one low-skew clock.

All parts of ASM3P623S00C have on-chip PLLs that lock to an input clock on the CLKIN pin. The PLL feedback is on-chip and is obtained from the CLKOUT pad, internal to ASM3P623S00C.Multiple ASM3P623S00D/E/F devices can accept the same input clock and distribute it. In this case, the skew between the outputs of the two devices is guaranteed to be less than 700pS.

All outputs of ASM3P623S00C have less than 200pS of cycle-to-cycle jitter.The input and output propagation delay is guaranteed to be less than 250pS, and the output-to-output skew is guaranteed to be less than 250pS.

Please refer "Differential Cycle Slips and Spread Spectrum Control Table" for deviations and differential Cycle Slips for ASM3P623S00A/B/C and the ASM3P623S00D/E/F devices The ASM3P623S00A/B/C and the ASM3P623S00D/E/F are available in two different configurations, as shown in the ordering information table.

ASM3P623S00C Data Sheet

ASM3P623S00C Data Sheet