Pinout Specifications

Specifications| Resolution | 10 bits |

| Channels | 2 Channels |

| SNR | 55.6 dB |

| SFDR | 66.7 dB |

| ENOB | 8.9 bits |

| Max Sample Rate | 1000 MSPS |

| Min Sample Rate | 200 MSPS |

| Power Dissipation | 2.9 Watt |

| PowerWise Rating 1 | 3.04 pJ/conv |

| DNL (+/-) | 0.2 LSB |

| INL (+/-) | 0.7 LSB |

| SINAD | 55.3 dB |

| THD dB | -67 dB |

| Min Supply Voltage | 1.8 Volt |

| Max Supply Voltage | 2.0 Volt |

| Nominal Vin | 0.82 Vpp |

| Temperature Min | -55 deg C |

| Temperature Max | 125 deg C |

| Data Converter Type | ADC |

| Automotive Selection Guide | No |

| PowerWise | Yes |

| Radiation Performance - Total Dose (TID) | 100 Krad |

| Radiation Performance - SEL (MeV) | >120 |

| View Using Catalog |

DescriptionThe ADC10D1000 is the latest advance in National's Ultra-High-Speed ADC family of products. This low-power, high-performance CMOS analog-to-digital converter digitizes signals at 10-bit resolution at sampling rates of up to 1.0 GSPS in dual channel mode or 2.0 GSPS in single channel mode. The ADC10D1000 achieves excellent accuracy and dynamic performance while consuming a typical 2.9 Watts of power. This space grade, Radiation Tolerant part is rad hard to a single event latch up level of greater than 120MeV and a total dose (TID) of 100 krad(Si). The product is packaged in a hermatic 376 column thermally enhanced CCGA package rated over the temperature range of -55°C to +125°C.

The ADC10D1000 builds upon the features, architecture and functionality of the 8-bit GHz family of ADCs. New features include an auto-sync feature for multi-chip synchronization, independent programmable 15-bit gain and 12-bit offset adjustment per channel, LC tank filter on the clock input, and the option of two's complement format for the digital output data. The unique folding and interpolating architecture, the fully differential comparator design, the innovative design of the internal track-and-hold amplifier and the self-calibration scheme enable a very flat response of all dynamic parameters beyond Nyquist, producing a high 8.9 Effective Number of Bits (ENOB) with a 498 MHz input signal and a 1.0 GHz sample rate while providing a 10 −18 Code Error Rate (C.E.R.) Consuming a typical 2.9 Watts in Non-Demultiplex Mode at 1.0 GSPS from a single 1.9 Volt supply, this device is guaranteed to have no missing codes over the full operating temperature range.

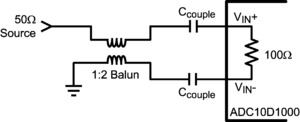

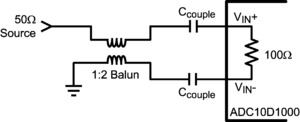

Each channel has its own independent DDR Data Clock, DCLKI and DCLKQ, which are in phase when both channels are powered up, so that only one Data Clock could be used to capture all data, which is sent out at the same rate as the input sample clock. If the 1:2 Demultiplexed Mode is selected, a second 10-bit LVDS bus becomes active for each channel, such that the output data rate is sent out two times slower, but two times wider to relax data-capture timing margin. The two channels (I and Q) can also be interleaved (DES Mode) and used as a single 2.0 GSPS ADC to sample on the Q input. The output formatting is offset binary or two's complement and the Low Voltage Differential Signaling (LVDS) digital outputs are compatible with IEEE 1596.3-1996, with the exception of an adjustable common mode voltage between 0.8V and 1.2V.

Reliability Metrics

| Part Number |

Process |

EFR Reject |

EFR Sample Size |

PPM |

LTA Rejects |

LTA Device Hours |

FITS |

MTTF (Hours) |

| ADC10D1000CCMLS |

CMOS9 |

1 |

6382 |

157 |

0 |

923000 |

4 |

261903770 |

Note: The Early Failure Rates (EFR) were calculated as point estimate PPM based on rejects and sample size for EFR. The Long Term Failure Rates were calculated at 60% confidence using the Arrhenius equation at 0.7eV activation energy and derating the assumed stress temperature of 150°C to an application temperature of 55°C.For more information on Reliability Metrics, please click here.

ADC10D1000QML Data Sheet

ADC10D1000QML Data Sheet