Features: 5 V Stereo Audio DAC System

Accepts 16-/18-/20-/24-Bit Data

Supports 24 Bits, 192 kHz Sample Rate

Accepts a Wide Range of Sample Rates Including:

32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, and 192 kHz

Multibit Sigma-Delta Modulator with "Perfect Differential

Linearity Restoration" for Reduced Idle Tones and

Noise Floor

Data Directed Scrambling DAC-Least Sensitive to Jitter

Single-Ended Output for Easy Use

108 dB Signal-to-Noise (Not Muted) at 48 kHz Sample

Rate (A-Weighted Stereo)

109 dB Dynamic Range (Not Muted) at 48 kHz Sample

Rate (A-Weighted Stereo)

96 dB THD + N (Stereo)

75 dB Stop Band Attenuation

On-Chip Clickless Volume Control

Hardware and Software Controllable Clickless Mute

Serial (SPI) Control for: Serial Mode, Number of Bits,

Sample Rate, Volume, Mute, De-Emphasis

Digital De-Emphasis Processing for 32 kHz, 44.1 kHz,

and 48 kHz Sample Rates

Programmable Dual Fractional-N PLL Clock Generator

27 MHz Master Clock Oscillator

Better than 100 ps rms Master Clock Jitter

Generated System Clocks

SCLK0: 33.8688 MHz

SCLK1: 22.5792 MHz, 24.576 MHz, 33.8688 MHz, or 36.864 MHz

SCLK2: 16.9344 MHz

Flexible Serial Data Port with Right-Justified, Left- Justified, I2S-Compatible, and DSP Serial Port Modes

28-Lead SSOP Plastic Package

APPLICATIONS

DVD, CD, Home Theater Systems, Automotive Audio

Systems, Sampling Musical Keyboards, Digital Mixing

Consoles, Digital Audio Effects ProcessorsApplicationDVD, CD, Home Theater Systems, Automotive Audio Systems, Sampling Musical Keyboards, Digital Mixing Consoles, Digital Audio Effects Processors

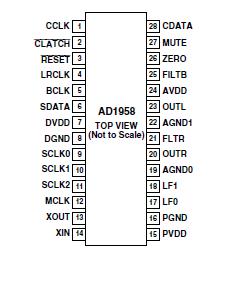

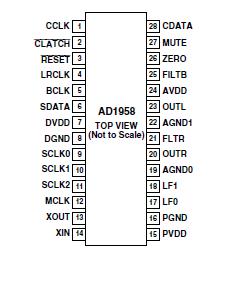

Pinout

SpecificationsDVDD to DGND . . . . . . . . . . . . . . . . . . . . . . 0.3 V to +6 V

SpecificationsDVDD to DGND . . . . . . . . . . . . . . . . . . . . . . 0.3 V to +6 V

AVDD to DGND . . . . . . . . . . . . . . . . . . . . . . 0.3 V to +6 V

Digital Inputs . . . . . . . . . . DGND 0.3 V to DVDD + 0.3 V

Analog Inputs . . . . . . . . . . AGND 0.3 V to AVDD + 0.3 V

AGND to DGND . . . . . . . . . . . . . . . . . . . . 0.3 V to + 0.3 V

Reference Voltage . . . . . . . . . . . . .. . . . . . . (AVDD + 0.3)/2

Soldering (10 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

| DAC DNR (dB) |

109dB |

| SNR (dB) |

108dB |

| DAC THD+N @ 1 kHz (-3dB) |

96dB |

| Product Description |

Stereo, 24-bit 192 kHz Multibit Sigma-Delta D/A w/ PLL |

DescriptionThe AD1958 has two DAC channels arranged as a stereo pair with single-ended analog outputs. Each channel has its own independently programmable attenuator, adjustable in 16384 linear steps. Digital inputs are supplied through a serial data input pin, SDATA, a frame clock, LRCLK, and a bit clock, BLCK.

Each analog output pin sits of AD1958 at a dc level of VREF (present at FILTR), and swings ± 1.585 V for a 0 dB digital input signal. A single op amp third-order external low-pass filter is recommended to remove high-frequency noise present on the output pins. The output phase can be changed in an SPI control register to accommodate inverting and noninverting filters. Note that the use of op amps with low slew rate or low bandwidth may cause high frequency noise and tones to fold down into the audio band; care should be exercised in selecting these components.

The FILTB and FILTR pins of AD1958 should be bypassed by external capacitors to ground. The FILTB pin is used to reduce the noise of the internal DAC bias circuitry, thereby reducing the DAC output noise. The voltage at the VREF pin, FILTR (VREF ~ 2.39 V) can be used to bias external op amps used to filter the output signals.

The DAC master clock frequency of AD1958 is 256 fS for the 32 kHz48 kHz range (8* interpolation, see Table I). For the 96 kHz range (4*interpolation) this is 128 fS. At 192 kHz (2* interpolation), this is 64 fS. It is supplied internally from the PLL clock system when MCLK mode is set to Output in the PLL Control Register.

When the MCLK mode is changed to Input, it must be supplied from an external source connected to MCLK. The output from the 27 MHz PLL clock is disabled in this case.

AD1958 Data Sheet

AD1958 Data Sheet