Features: •ESD protection:

HBMEIA/JESD22-A114-Aexceeds 2000V

MMEIA/JESD22-A115-A exceeds 200V

CDMEIA/JESD22-C101 exceeds 1000V

•Balanced propagation delays

•All inputs have Schmitt-trigger actions

•Inputs accepts voltages higher than VCC

•Common 3-state output enable input

•Functionally identical to the '533', '563' and '573'

•For AHC only: operates with CMOS input levels

•For AHCT only: operates with TTL input levels

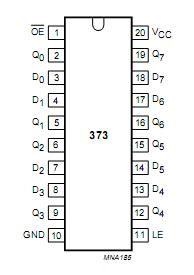

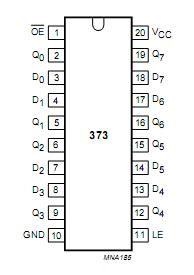

•Specified from −40 to+85°C and−40 to+125°C.Pinout Description

DescriptionThe 74AHCT373 are high-speed Si-gate CMOS devices and are pin compatible with Low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no.7A.

The 74AHCT373 are octal D-type transparent latches featuring separate D-type inputs for each latch and 3-state outputs for bus oriented applications. A Latch Enable(LE) input and an Output Enable(OE</a>) input are common to all latches.

The'373'consists of eight D-type transparent latches with 3-state true outputs. WhenLE is HIGH, data at the Dn inputs enters the latches. In this condition the latches are transparent, i.e. a latch output will change state each time its corresponding D-input changes.

When LE is LOW the latches store the information that was present at the D-inputs a set-up time preceding the HIGH-to-LOW transition ofLE. When OE</a> is LOW, the contents of the 8latches are available at the outputs. When OE</a> is HIGH, the outputs go to the high-impedance OFF-state. Operation of the OE</a> input does not affect the state of the latches.

The '373' is functionally identical to the '533', '563' and '573',butthe'533'and'563'have inverted outputs and the '563' and '573' have a different pin arrangement.

74AHCT373 Data Sheet

74AHCT373 Data Sheet