Features: `ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V CDM EIA/JESD22-C101 exceeds 1000 V

`All inputs have Schmitt-trigger actions

`Inputs accept voltages higher than VCC

`For AHC only: operates with CMOS input levels

`For AHCT only: operates with TTL input levels

`Specified from -40 to +85 and -40 to +125

`DC triggered from active HIGH or active LOW inputs

`Retriggerable for very long pulses up to 100% duty factor

`Direct reset terminates output pulse

`Output capability: standard (except for nREXT/CEXT).

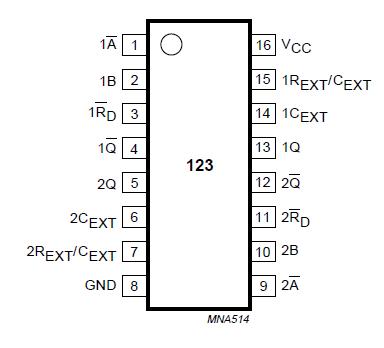

Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

| VCC |

DC supply voltage |

|

-0.5 |

+7.0 |

V |

| VI |

input voltage |

|

-0.5 |

+7.0 |

V |

| IIK |

DC input diode current |

VI < -0.5 V; note 1 |

- |

-20 |

mA |

| IOK |

DC output clamping diode current |

VO < -0.5 V or VO > VCC + 0.5

V; note 1 |

- |

±20 |

mA |

| IO |

DC output sink current |

-0.5 V < VO < VCC + 0.5 V |

- |

±25 |

mA |

| ICC |

DC VCC or GND current |

|

- |

±75 |

mA |

| Tstg |

storage temperature |

|

-65 |

+150 |

|

| PD |

power dissipation per package |

for temperature range:

-40 to +125 ; note 2 |

- |

500 |

mW |

DescriptionThe 74AHCT123A are high-speed Si-gate CMOS devices and are pin compatible with Low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no.7A.

The 74AHCT123A are dual retriggerable monostable multivibrators with output pulse width control by three methods. The basic pulse time is programmed by selection of an external resistor (REXT) and capacitor (CEXT). The external resistor and capacitor are normally connected as shown in Fig.6.

Once triggered, the basic output pulse width may be extended by retriggering the gated active LOW-going edge input (nA ) or the active HIGH-going edge input (nB). By repeating this process, the output pulse period (nQ = HIGH, nQ = LOW) can be made as long as desired. Alternatively an output delay can be terminated at any time by a LOW-going edge on input nRD, which also inhibits the triggering.

An internal connection of the 74AHCT123A from nRD to the input gate makes it possible to trigger the circuit by a positive-going signal at input nRD as shown in the function table. Figs 8 and 9 illustrate pulse control by retriggering and early reset. The basic output pulse width is essentially determined by the value of the external timing components REXT and CEXT. When CEXT ³ 10 nF, the typical output pulse width is defined as: tW = REXT ´ CEXT where tW = pulse width in ns; REXT = external resistor in kW; CEXT = external capacitor in pF. Schmitt-trigger action at all inputs makes the circuit highly tolerant to slower input rise and fall times. The '123' is identical to the '423' but can be triggered via the reset input.

74AHCT123A Data Sheet

74AHCT123A Data Sheet