Features: •Two sets of high speed parallel registers with positive edge-triggered D-type flip-flops

•Ideal where high speed, light loading, or increased fan-in are required with MOS microprocessors

•Live insertion/extraction permitted

•Power-up 3-State

•74ABTH16823A incorporates bus-hold data inputs which eliminate the need for external pull-up resistors to hold unused inputs

•Power-up Reset

•Output capability: +64mA/32mA

•Latch-up protection exceeds 500mA per Jedec Std 17

•ESD protection exceeds 2000 V per MIL STD 883 Method 3015 and 200 V per Machine Model

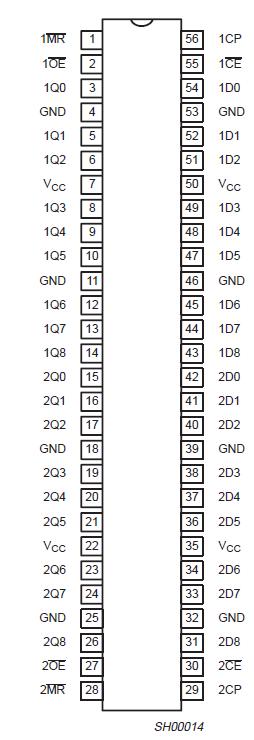

Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

RATING |

UNIT |

| VCC |

DCsupplyvoltage |

|

0.5to+7.0 |

V |

| IIK |

DCinputdiodecurrent |

VI < 0 |

18 |

mA |

| VI |

DC input voltage3 |

|

1.2to+7.0 |

V |

| IOK |

DCoutputdiodecurrent |

VO < 0 |

50 |

mA |

| VOUT |

DC output voltage3 |

outputinOfforHighstate |

0.5to+5.5 |

V |

| IOUT DC output current |

output in Low state |

128 |

mA |

| output in High state |

64 |

| Tstg |

Storagetemperaturerange |

|

65 to 150 |

|

DescriptionThe 74ABTH16823A 18-bit bus interface register is designed to eliminate the extra packages required to buffer existing registers and provide extra data width for wider data/address paths of buses carrying parity.

The 74ABTH16823A has two 9-bit wide buffered registers with Clock Enable (nCE ) and Master Reset (nMR) which are ideal for parity bus interfacing in high microprogrammed systems.

The registers of the 74ABTH16823A are fully edge-triggered. The state of each D input, one set-up time before the Low-to-High clock transition is transferred to the corresponding flip-flop's Q output.

Two options are available, 74ABTH16823A which does not have the bus-hold feature and 74ABTH16823A which incorporates the bus-hold feature.

74ABTH16823A Data Sheet

74ABTH16823A Data Sheet