Features: • Low static and dynamic power dissipation with high speed and high output drive

• Open-collectorERROR output

• Output capability: +64mA/32mA

• Latch-up protection exceeds 500mA per Jedec Std 17

• ESD protection exceeds 2000 V per MIL STD 883 Method 3015 and 200 V per Machine Model

• Power-up 3-State

• Live insertion/extraction permittedPinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

RATING |

UNIT |

| VCC |

DC supply voltage |

|

0.5 to +7.0 |

V |

| IIK |

DC input diode current |

VI < 0 |

18 |

mA |

| VI |

DC input voltage3 |

|

1.2 to +7.0 |

V |

| IOK |

DC output diode current |

VO < 0 |

50 |

mA |

| VOUT |

DC output voltage3 |

output in Off or High state |

0.5 to +5.5 |

V |

| IOUT |

DC output current |

output in Low state |

128 |

mA |

| Tstg |

Storage temperature range |

|

65 to 150 |

°C |

NOTES:

1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

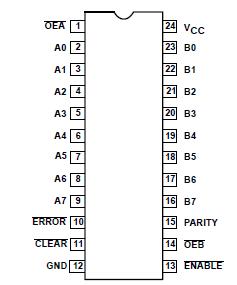

DescriptionThe 74ABT853 is an octal transceiver with a parity generator/checker and is intended for busoriented applications.

When Output Enable A (OEA) is High, it will place the A outputs in a high impedance state. Output Enable B (OEB) controls the B outputs in the same way.

The parity generator creates an odd parity output (PARITY) when OEB is Low. When OEA is Low, the parity of the B port, including the PARITY input, is checked for odd parity. When an error is detected, the error data is sent to the input of a latch. The error data can then be passed, stored, cleared, or sampled depending on the ENABLE and CLEAR control signals.

If both OEA and OEB are Low, data of the 74ABT853 will flow from the A bus to the B bus and the part is forced into an error condition which creates an inverted PARITY output. This error condition can be used by the designer for system diagnostics.

74ABT853 Data Sheet

74ABT853 Data Sheet