Low Level Output Current

:

Number of Circuits

: 8

Minimum Operating Temperature

: - 40 C

Polarity

: Non-Inverting

Number of Output Lines

: 3

Supply Voltage - Max

: 5.5 V

Maximum Operating Temperature

: + 85 C

Package / Case

: PDIP-20

Packaging

: Tube

Supply Voltage - Min

: 4.5 V

Logic Type

: Transparent Latch

Logic Family

: 74ABT

High Level Output Current

: - 32 mA

Propagation Delay Time

: 4.5 ns at 5 V

Features: 3-STATE outputs for bus interfacing

Output sink capability of 64 mA, source capability of 32 mA

Guaranteed output skew

Guaranteed multiple output switching specifications

Output switching specified for both 50 pF and 250 pF loads

Guaranteed simultaneous switching, noise level and dynamic threshold performance

Guaranteed latchup protection

High impedance glitch free bus loading during entire power up and power down

Nondestructive hot insertion capabilityPinout SpecificationsStorage Temperature .........................−65°C to +150°C

SpecificationsStorage Temperature .........................−65°C to +150°C

Ambient Temperature under Bias....... −55°C to +125°C

Junction Temperature under Bias....... −55°C to +150°C

VCC Pin Potential to Ground Pin............. −0.5V to +7.0V

Input Voltage (Note 2)........................... −0.5V to +7.0V

Input Current (Note 2) ....................−30 mA to +5.0 mA

Voltage Applied to Any Output

in the Disabled or

Power-Off State................................. −0.5V to +5.5V

in the HIGH State ..................................−0.5V to VCC

Current Applied to Output

in LOW State (Max).............. twice the rated IOL (mA)

DC Latchup Source Current: OE Pin.................. −150 mA

(Across Comm Operating Range) Other Pins.−500 mA

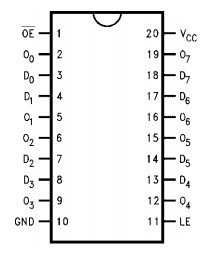

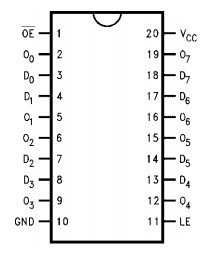

Over Voltage Latchup (I/O)...................................... 10VDescriptionThe 74ABT373CPC consists of eight latches with 3-STATE outputs for bus organized system applications. The flip-flops appear transparent to the data when Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the setup times is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH the bus output is in the high impedance state.

74ABT373CPC Data Sheet

74ABT373CPC Data Sheet