Side 1 Body Style

:

Side 2 Body Style

:

Impedance

:

Frequency Range

:

Side 1 Polarity

: Normal

Side 2 Polarity

: Normal

Adapter Style

: Straight

Contact Plating

: Gold

Body Material

: Brass

Side 1 Gender

: Plug (Male)

Side 2 Gender

: Plug (Male)

Side 1 RF Series

: BNC

Shell Plating

: Nickel

Side 2 RF Series

: Mini-Weco

Features: • Fast access times: 3.5, 3.8, and 4.0ns

• Fast clock speed: 166, 150, 133, and 117MHz

• Provide high performance 3-1-1-1 access rate

• Fast OE# access times: 3.5ns and 3.8ns

• Optimal for depth expansion (one cycle chip deselect to liminate bus contention)

• 3.3V -5% and +10% core power supply

• 2.5V or 3.3V I/O supply

• 5V tolerant inputs except I/O's

• Clamp diodes to VSSQ at all inputs and outputs

• Common data inputs and data outputs

• BYTE WRITE ENABLE and GLOBAL WRITE control

• Three chip enables for depth expansion and address ipeline

• Address, data and control registers

• Internally self-timed WRITE CYCLE

• Burst control pins (interleaved or linear burst sequence)

• Automatic power-down for portable applications

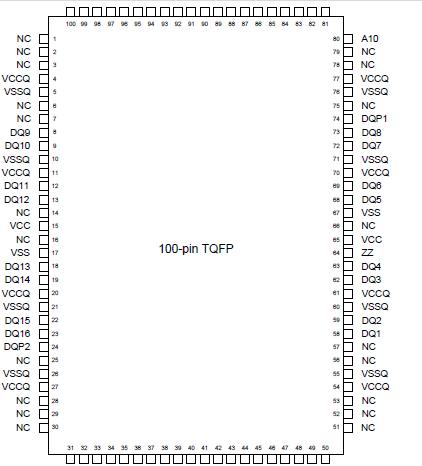

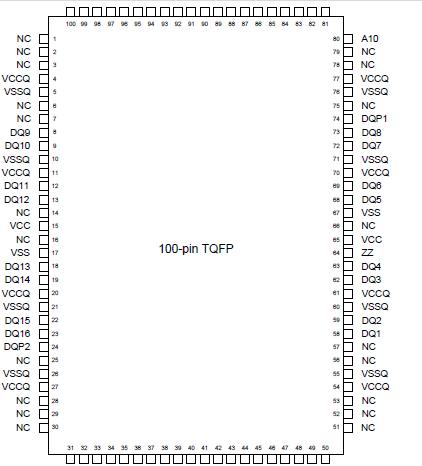

• High density, high speed packagesPinout Specifications

SpecificationsVoltage on VCC Supply Relative to VSS..... . -0.5V to +4.6V

VIN ...........................................................-0.5V to VCC+0.5V

Storage Temperature (plastic) ......................-55oC to +150o

Junction Temperature ..................................................+150o

Power Dissipation ..........................................................1.0W

Short Circuit Output Current ..........................................50mA

*Stresses greater than those listed uunder "Absolute Maximum atings" may cause permanent damage to the device.This is a stress ating only and functional operation of the device at these or any ther conditions above those indicated in the operational sections of his specification is not implied. Exposure to absolute maximum ating conditions for extended periods may affect reliability.

DescriptionThe Galvantech Synchronous Burst SRAM family mploys of 6519 high-speed, low power CMOS designs using dvanced triple-layer polysilicon, double-layer metal echnology. Each memory cell consists of four transistors and wo high valued resistors.

The 6519 SRAM integrates 262,144x18 RAM cells with advanced synchronous peripheral circuitry nd a 2-bit counter for internal burst operation. All ynchronous inputs are gated by registers controlled by a ositive-edge-triggered clock input (CLK). The synchronous nputs include all addresses, all data inputs, address-pipelining hip enable (CE#), depth-expansion chip enables (CE2# and E2), burst control inputs (ADSC#, ADSP#, and ADV#), rite enables (WEL#, WEH#, and BWE#), and global write GW#).

Asynchronous inputs of 6519 include the output enable (OE#) nd burst mode control (MODE). The data outputs (Q),enabled by OE#, are also asynchronous.

Addresses and chip of 6519 enables are registered with either ddress status processor (ADSP#) or address status controller ADSC#) input pins. Subsequent burst addresses can be nternally generated as controlled by the burst advance pin ADV#).

Address, data inputs, and write controls of 6519 are registered onchip o initiate self-timed WRITE cycle. WRITE cycles can e one to four bytes wide as controlled by the write control nputs. Individual byte write allows individual byte to be ritten. WEL# controls DQ1-DQ8 and DQP1. WEH# ontrols DQ9-DQ16 and DQP2. WEL#, and WEH# can be ctive only with BWE# being LOW. GW# being LOW causes ll bytes to be written. WRITE pass-through capability allows ritten data available at the output for the immediately next EAD cycle. This device also incorporates pipelined enable ircuit for easy depth expansion without penalizing system erformance.

The 6519 operates from a +3.3V core power upply and all outputs operate on a +2.5V supply. All inputs nd outputs are JEDEC standard JESD8-5 compatible. The evice is ideally suited for 486, PentiumTM, 680x0, and owerPCTM systems and for systems that are benefited from a ide synchronous data bus.

Parameters: | Technical/Catalog Information | 6519 |

| Vendor | Pomona Electronics |

| Category | Connectors |

| Color | - |

| Convert From (Adapter End) | BNC Jack, Female Socket |

| Convert To (Adapter End) | WECo, Mini |

| Features | - |

| Lead Free Status | Lead Free |

| RoHS Status | RoHS Compliant |

| Other Names | 6519

6519

|

6519 Data Sheet

6519 Data Sheet