Ranging

: Auto, Manual

True RMS

: Yes

Data Hold

: No

Display Count

: 50000

Resistance Range

: 500 Ohms to 50 MOhms

Frequency

: 5 Hz to 200 KHz

Accuracy

: +/- 0.03 %

Voltage Range

: 5 V to 1000 V

Capacitance Range

: 50 nF to 5000 uF

Features: • Zero Bus Latency, no dead cycles between write and read cycles

• Fast clock speed: 200, 166, 133, and 100MHz

• Fast access time: 3.2, 3.6, 4.2, 5.0ns

• Internally synchronized registered outputs eliminate the need to control OE#

• Single 3.3V -5% and +5% power supply VCC

• Separate VCCQ for 3.3V or 2.5V I/O

• Single R/W# (READ/WRITE) control pin

• Positive clock-edge triggered, address, data, and control signal registers for fully pipelined applications

• Interleaved or linear 4-word burst capability

• Individual byte write (BWa# - BWd#) control (may be tied LOW)

• CKE# pin to enable clock and suspend operations

• Three chip enables for simple depth expansion

• SNOOZE MODE for low power standby

• JTAG boundary scan

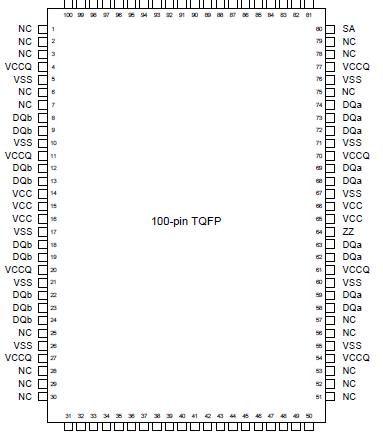

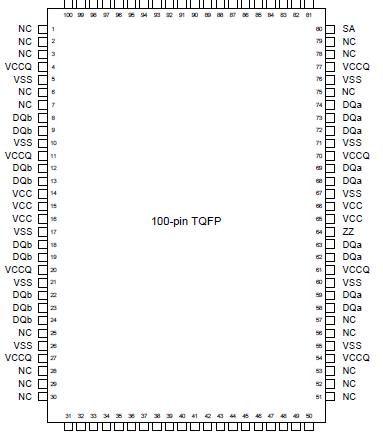

• Low profile 119 bump, 14mm x 22mm PBGA (Ball Grid Array) and 100 pin TQFP packagesPinout Specifications

SpecificationsVoltage on VCC Supply Relative to VSS........ -0.5V to +4.6V

VIN ...........................................................-0.5V to VCC+0.5V

Storage Temperature (plastic) .......................-55oC to +125o

Junction Temperature ...................................................+125o

Power Dissipation ...........................................................2.0W

Short Circuit Output Current ..........................................50mA

*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

DescriptionThe GVT71256ZC36 and GVT71512ZC18 SRAMs are designed to eliminate dead cycles when transitions from READ to WRITE or vice versa. These SRAMs are optimized for 100 percent bus utilization and achieves Zero Bus Latency (ZBL). They integrate 262,144x36 and 524,288x18 SRAM cells, respectively, with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation. The Galvantech Synchronous Burst SRAM family employs highspeed,low power CMOS designs using advanced triple-layer polysilicon, double-layer metal technology. Each memory cell consists of four transistors and two high valued resistors.

All synchronous inputs are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs include all addresses, all data inputs, depth-expansion chip enables (CE#, CE2# and CE2), cycle start input (ADV/LD#), clock enable (CKE#), byte write enables (BWa#, BWb#, BWc# and BWd#), and read-write control (R/W#). BWc# and BWd# apply to GVT71256ZC36 only.

Address and control signals are applied to the SRAM during one clock cycle, and two cycles later, its associated data occurs, either read or write.

A clock enable (CKE#) pin allows operation of the GVT71256ZC36/GVT71512ZC18 to be suspended as long as necessary. All synchronous inputs are ignored when (CKE#) is high and the internal device registers will hold their previous values.

There are three chip enable pins (CE#, CE2, CE2#) that allow the user to deselect the device when desired. If any one of these three are not active when ADV/LD# is low, no new memory operation can be initiated and any burst cycle in progress is stopped. However, any pending data transfers (read or write) will be completed. The data bus will be in high impedance state two cycles after chip is deselected or a write cycle is initiated.

The GVT71256ZC36 and GVT71512ZC18 have an onchip 2-bit burst counter. In the burst mode, the GVT71256ZC36 and GVT71512ZC18 provide four cycles of data for a single address presented to the SRAM. The order of the burst sequence is defined by the MODE input pin. The MODE pin selects between linear and interleaved burst sequence. The ADV/LD# signal is used to load a new external address (ADV/LD#=LOW) or increment the internal burst counter (ADV/LD#=HIGH) Output enable (OE#), snooze enable (ZZ) and burst sequence select (MODE) are the asynchronous signals. OE# can be used to disable the outputs at any given time. ZZ may be tied to LOW if it is not used.

Four pins are used to implement JTAG test capabilities.

The JTAG circuitry is used to serially shift data to and from the device. JTAG inputs use LVTTL/LVCMOS levels to shift data during this testing mode of operation.

Parameters: | Technical/Catalog Information | 6500 |

| Vendor | Paladin Tools |

| Category | Tools |

| For Use With/Related Products | General Purpose |

| Tool Type | Multi-tool |

| Lead Free Status | Lead Free |

| RoHS Status | RoHS Compliant |

| Other Names | 6500

6500

PAL6500 ND

PAL6500ND

PAL6500

|

6500 Data Sheet

6500 Data Sheet