Output Type

: 3-State

Maximum Operating Temperature

: + 85 C

Low Level Output Current

: 24 mA

Number of Channels per Chip

: 4

Input Level

: TTL

High Level Output Current

: - 3 mA

Logic Type

: ECL

Output Level

: ECL

Propagation Delay Time

: 5.1 ns

Packaging

: Rail

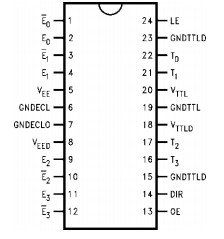

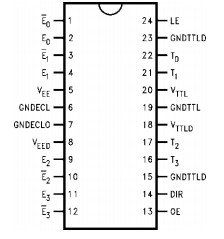

Package / Case

: DIP-24

Supply Voltage - Max

: - 5.7 V, + 5.5 V

Supply Voltage - Min

: - 4.2 V, + 4.5 V

Logic Family

: 100

Features: Differential ECL input/output structure

64 mA FAST TTL outputs

25Ω differential ECL outputs with cut-off

Bi-directional translation

2000V ESD protection

Latched outputs

3-STATE outputs

Voltage compensated operating range = −4.2V to −5.7VPinout SpecificationsStorage Temperature (TSTG)............. −65°C to +150°C

SpecificationsStorage Temperature (TSTG)............. −65°C to +150°C

Maximum Junction Temperature

(TJ)............................................................... +150°C

VEE Pin Potential to Ground Pin .............−7.0V to +0.5V

VTTL Pin Potential to Ground Pin ...........−0.5V to +6.0V

ECL Input Voltage (DC)............................. VEE to +0.5V

ECL Output Current

(DC Output HIGH) .........................................−50 mA

TTL Input Voltage (Note 7).................... −0.5V to +7.0V

TTL Input Current (Note 7) .............−30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State

3-STATE Output................................. −0.5V to +5.5V

Current Applied to TTL

Output in LOW State (Max) twice the Rated IOL (mA)

ESD (Note 6) .....................................................2000VDescriptionThe 100397 is a quad latched transceiver designed to convert TTL logic levels to differential F100K ECL logic levels and vice versa. This device was designed with the capability of driving a differential 25Ω ECL load with cutoff capability, and will sink a 64 mA TTL load. The 100397 is ideal for mixed technology applications utilizing either an ECL or TTL backplane.

The direction of translation is set by the direction control pin (DIR). The DIR pin on the 100397 accepts F100K ECL logic levels. An ECL LOW on DIR sets up the ECL pins as inputs and TTL pins as outputs. An ECL HIGH on DIR sets up the TTL pins as inputs and ECL pins as outputs.

A LOW on the output enable input pin (OE) holds the ECL output in a cut-off state and the TTL outputs at a high impedance level. A HIGH on the latch enable input (LE) latches the data at both inputs even though only one output is enabled at the time. A LOW on LE makes the latch transparent.

The cut-off state is designed to be more negative than a normal ECL LOW level. This allows the output emitterfollowers to turn off when the termination supply is −2.0V, presenting a high impedance to the data bus. This high impedance reduces termination power and prevents loss of low state noise margin when several loads share the bus.

The 100397 is designed with FAST TTL output buffers, featuring optimal DC drive and capable of quickly charging and discharging highly capacitive loads. All inputs have 50 KΩ pull-down resistors.

100397PC Data Sheet

100397PC Data Sheet