Signal Processing

ULTRA_FAST_MONOCYCLE_GENERATOR_

Published:2009/7/14 7:03:00 Author:May | From:SeekIC

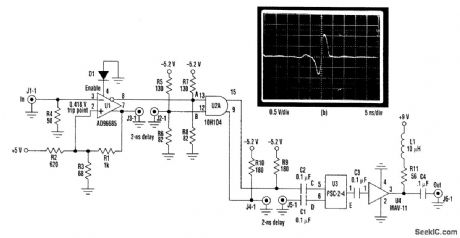

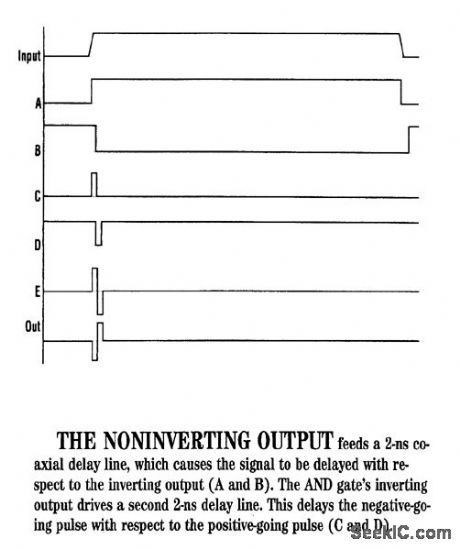

This circuit (Fig. 1a) can test an ultra-fast sample-and-hold amplifier, producing the monocycle shown (Fig.1b) when triggered with a TTL input pulse. The comparator (U1) squares up the input pulse and drives the AND gate (U2) with complementary outputs. The hysteresis resistors are chosen to provide reliable triggering despite the 50-Ω loading of the TTL input. The noninverting comparator output feeds a 2-ns coaxial delay line, causing the signal to be delayed with respect to the inverting output (Fig. 2). This forces the outputs of the AND gate to change state for a period of time equal to the delay. The inverting output of the AND gate drives a second 2-ns delay line, delaying the negative-going pulse, with respect to the positive-going pulse (Fig. 2). The power combiner (U3) sums the signals, producing a monocycle output. U4 amplifies the signal. Shorter pulses could be produced by shortening the delay lines and replacing U2 with an AND gate from a faster ECL family.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Signal_Processing/ULTRA_FAST_MONOCYCLE_GENERATOR_.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: