Signal Processing

The odd-even frequency splitter composed of SN74193

Published:2011/6/17 22:14:00 Author:Borg | Keyword: frequency splitter | From:SeekIC

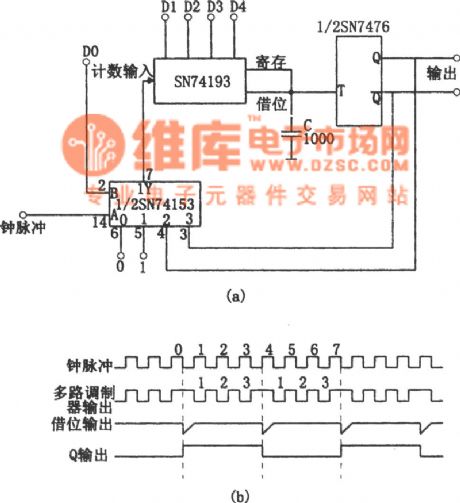

In the figure is the odd-even frequency splitter circuit. This circuit can engage in 2~32 (including odd and even) times of splitting. The counting input of the synchronized counter SN74193 is provided by the output 1Y of the multiplexer SN74153, the borrow output of the counter can not only drive the trigger SN7476, but also it's the deposit input pulse of SN74193. The 5-bit binary numbers are imposed on D0, D1, D3 and D4 input terminals, which decides the splitting constant(2~32), and D0 is the lowest bit. When D0=0, the outputting pulse phase of the multiplexer is determined according to the trigger state.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Signal_Processing/The_odd_even_frequency_splitter_composed_of_SN74193.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: