Signal Processing

ACOUSTIC_FIELD_GENERATOR

Published:2009/6/22 22:35:00 Author:May | From:SeekIC

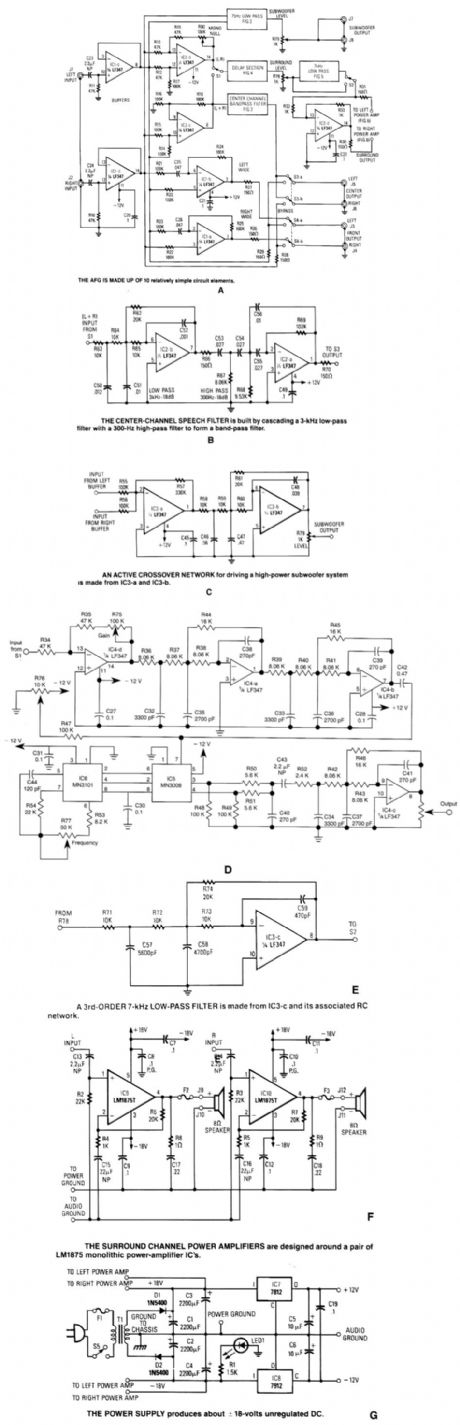

Referring to the simplified schematic in A, the AFG is made up of 10 relatively simple circuit el-ements. ICl-c and ICl-d are configured as unity-gain noninverting buffer amplifiers.

The summing (L+R) amplifier, IC2-c, combines equal amounts of the left and right signals, via R14 and R15, to develop a total composite signal. Left- and right-channel signals are applied equally through R13 and R12 to IC2-d, the difference (L-R) decoder. Any common to both channels is canceled by IC2-d, which exactly balances the inverting and noninverting gains of the amplifier for a perfect null.

The stereo width-enhancement circuit made up from IC1-a and IC-b works similarly to the (L-R) decoder, except that C25 and C26 have been added in the inverting inputs of each op amp. IC1-b de-velops the left wide signal because its inverting and noninverting inputs are connected to the left

and right channels opposite that of IC1-a. The output of the width-enhancement circuit is routed to 54, which selects either the wide or the bypass signal for feeding the front-channel amplifier.

The center-channel dialogue filter is built by cascading a 3-kHz low-pass filter with a 3-Hz high-pass filter to form a band-j:ass filter. It has a sharp -18 dB/octave cutoff, a flat voltage and power fre-quency response, and minimum phase change within the passband.

In C, IC3-a and IC3-b form an active crossover network for driving a subwoofer. IC3-a sums sig-nals from the left- and right-channel buffer amps, it inverts the summed signal 180 degrees, and pro-vides a low driving impedance for the following filter stage. IC3-b and its associated RC network form a 75-Hz, 3rd-order low-pass filter. The filter inverts the signal another 180 degrees, so the signal that appears across R79 (which is the output-level control) is back in phase with the original input signal.

The delay section of the AFG, shown in D, is built around the MN3008 bucket brigade device (BBD), and the MN3101 two-phase variable-frequency clock generator. The amount of delay re-quired in this system varies between approximately 5 to 35 milliseconds. The delay time of a BBD is equal to the number of stages divided by twice the clock frequency. Values were chosen for R53, R54, R77, and C44, to produce a clock frequency, adjustable via R77, which varies from about 30 kHz to 130 kHz.

In A, S1 selects the signal to be delayed, either the difference signal (L-R) from IC2-djn the ma-Lrix mode or the sum signa! (L-R) from IC2-c in the concert mode. The selected signal is fed from S1 to the delay section (D) where IC4-d is configured as an inverting amplifier; R75 adjusts the gain between unity and X3: Integrated circuits IC4-a and IC4-b, along with their assoicated RC networks: are identical 3rd-order 15-kHz low-pass filters. Cascading two filters produces a very sharp cut off (-36 dB per octave). Potentiometer R76 adjusts the bias voltage required by the BBD to exactly one half the supply voltage, as required.

The power suppty of the AFG, shown in G, is of conventional design. A 25-V center-tapped trans-former, along with diodes D1 and D2, produces about t18-V unregulated dc. 1bro 2200-μF filter capacitors provide ample energy storage to meet the high-current demands of the audio output amplifier ICs during high output peaks.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Signal_Processing/ACOUSTIC_FIELD_GENERATOR.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: