power supply circuit

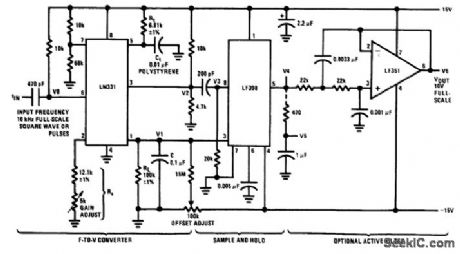

F_V_converter_with_sample_hold_and_active_filter

Published:2009/7/23 23:54:00 Author:Jessie | From:SeekIC

Fig, 12-20 This circuit uses both a sample/hold and an active filter to minimize the ripple/response tradeoff. With the values shown, ripple (at V6) is about 1 mVp-p. Response or settling time to a step change of input frequency is about 60 ms. Linearity is better than 0.1% from 10 kHz down to 500 Hz, but becomes increasingly nonlinear below 500 Hz. To trim, apply 1 kHz and set the offset adjust for 1-V output. Then, apply 10 kHz and set the gain adjust for 10-V Output. National Semiconductor. Linear Applications Handbook 1991,p 1253.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Power_Supply_Circuit/F_V_converter_with_sample_hold_and_active_filter.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: