Basic Circuit

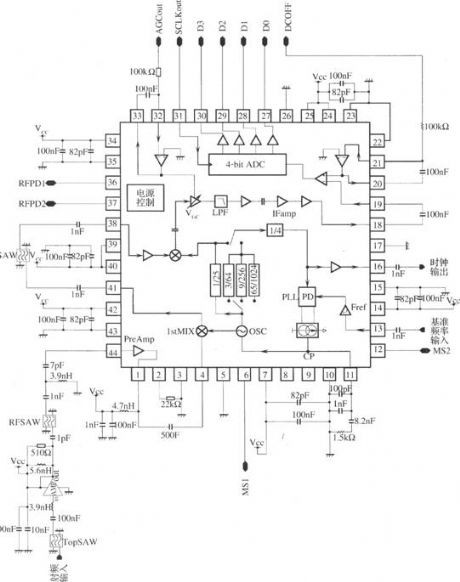

μPB1009K - based GPS receiver RF front-end circuit

Published:2012/8/25 1:28:00 Author:Ecco | Keyword: GPS receiver , RF front-end | From:SeekIC

μPBl009K is a single-chip GPS receiver chip which integrates full VCO, the second stage IF ( intermediate frequency ) filter, 4bit ADC, digital control interface circuit.μPBl009K has the double conversion function: fREFin = 16.368 MHz f1stFin = 61.380MHz f2dFin = 4.092 MHz ; fREFin 14.4/16.384/19.2/26MHz f1stFin = 62.980MHz f2ndIFin = 2 . 556MHz. It has a multi - system clock. With frequency divider ( 1 / N = 100,3 / 256,9 / 1024,65 / 4096 ) on the conversion sheet, TCXO frequency can be 16.368MHz/16.384MHz, 14.4MHz, 19 .2 MHz, or 26MHz. The power supply voltage Vcc = 2.7V - 3.3V. Low current consumption : lcc = 26.0mA.μPBl009K can be applied to the GPS receiver with reference frequency in 16.368MHz, the second-stage IF frequency in 4.092MHz, and the GPS receiver with reference frequency in 14.4MHz , 16.384MHz, 19.2MHz and 26MHz, the second-stage IF frequency in 2.556MHz.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/μPB1009K___based_GPS_receiver_RF_front_end_circuit.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: