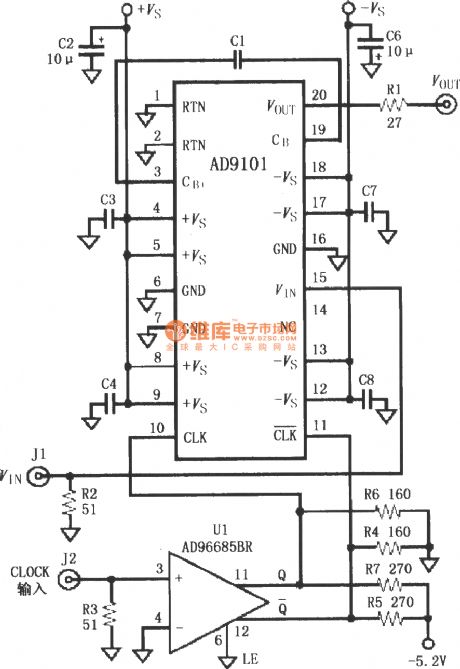

Basic Circuit

The basic connection circuit of sample and hold amplifier AD9101

Published:2012/8/24 22:00:00 Author:Ecco | Keyword: basic connection , sample and hold , amplifier | From:SeekIC

AD9101 is built-in the holding capacitor CHOLD, and sample-and-hold is controlled by the CLOCK. According to basic connection diagram, RTN grounds to keep the gain of the amplifier in 4. The noninverting input terminal of ultrafast comparator AD96685BR produced by the Analog Devices Inc. is added the clock input, then Q is sent to AD9100's non CLK and CLK (10,11 feet) as the sampling and holding control signal. The capacitors without marking use 0.01μF; the selection of R1 should be subject to the load capacitor with considering the condition that load capacitance may be less than 6pF in short circuit.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/The_basic_connection_circuit_of_sample_and_hold_amplifier_AD9101.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: