About SeekIC | Services | Payment | Advertisements service | Contact Us | Links

© 2008-2012 SeekIC.com Corp.All Rights Reserved.

Published:2009/7/6 3:27:00 Author:May | From:SeekIC

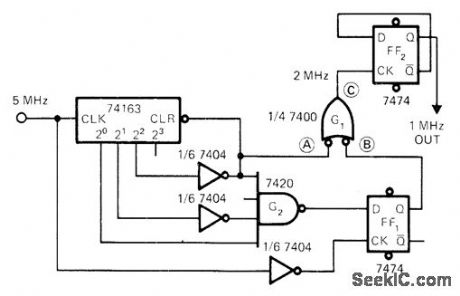

Uses 74163 counter to generate two phases of 1-MHz clock pulse with 50% duty cycle from 5-MHz system reference. One phase is decode of binary 4 from counter, while other is decode of 1 clocked at midbit time. Both phases are recombined in gate G1 to give 2-MHz clock that toggles FF2 to generate desired 1-MHz output.-L. A.Mann, Divider Circuit Maintains Pulse Symmetry, EDN Magazine, July 1, 1972, p 54-55.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/SYMMETRICAL_DIVIDE_BY_5_CLOCK.html

Print this Page | Comments | Reading(3)

Response in 12 hours

© 2008-2012 SeekIC.com Corp.All Rights Reserved.

Code: