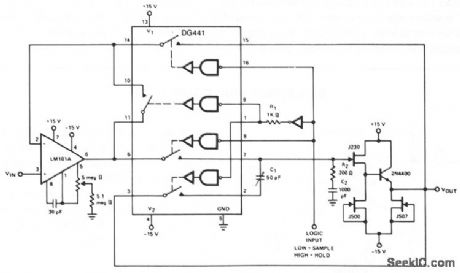

Basic Circuit

SAMPLE_AND_HOLD_2

Published:2009/7/9 23:15:00 Author:May | From:SeekIC

The LM101A provides gain and buffers the input from storage capacitor C2. R2 adds a zero in the open loop response to compensate for the pole caused by the switch resistance and C2, improving the closed-loop stability. R1 provides a slight delay in the digital drive to pins 1 and 9. C1 provides cancellation of coupled charge, keeping the sample-and-hold offset below 5 mV over the analog signal range of -10 through + 10 V. Aperture time is typically 1 pts, the switching time of the DG441. Acquisition time is 25 μs, but this can be improved by using a faster slewing op amp. Droop rate is typically less than 5 mV/s at 25℃.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/SAMPLE_AND_HOLD_2.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: