Basic Circuit

ODD_NUMBER_COUNTER_DIVIDER

Published:2009/7/6 20:20:00 Author:May | From:SeekIC

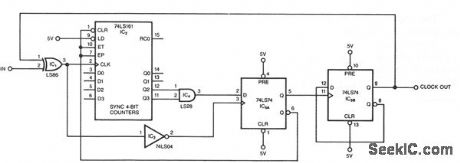

This circuit, shown symmetrically, divides an input by virtually any odd number. The circuit counts n + 1/2 clocks twice to achieve the desired divisor. By selecting the proper n, which is the decoded output of the LS161 counter, you can obtain divisors front 3 to 31. The circuit, as shown, divides by 25; you can obtain higher divisors by cascading additional LS161 counters. The counter and IC5A form the n + 1/2 counter. Once the counter reaches the decoded count, n, IC5A ticks off an additional 1/2 clock, which clears the counter and puts it in hold. Additionally, IC5A clocks IC5B, which changes the clock phasing through the XOR gate, IC1. The next edge of the input clocks IC5A, which reenables the counter to start counting for an additional n + 1/2 cycles. Although the circuit has been tested at 16 MHz, a worst-case timing analysis reveals that the maximum input frequency is between 7 and 8 MHz.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/ODD_NUMBER_COUNTER_DIVIDER.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: