Basic Circuit

Microprocessor_interface_for_free_running_A_D

Published:2009/7/23 22:39:00 Author:Jessie | From:SeekIC

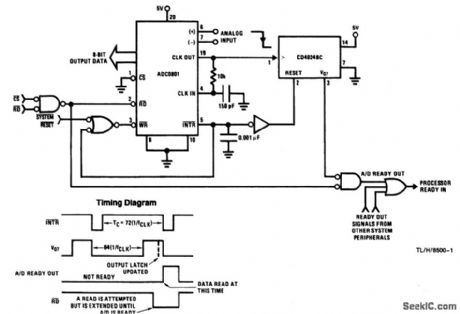

This circuit provides for asynchronous reads of analog data to an 8-bit microprocessor. The CD4024BC ripple counter generates a READY signal to the microprocessor that prevents a READ during a data update. The output data latches are updated one A/D-clock period before the INTR falls low, and the free-running conversion time is always 72 clock periods long. To start the A/D converter, a logic low must be applied to the SYSTEM RESET. The timing diagram shows relationships of the INTR, READY, and RDsignals.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/Microprocessor_interface_for_free_running_A_D.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: