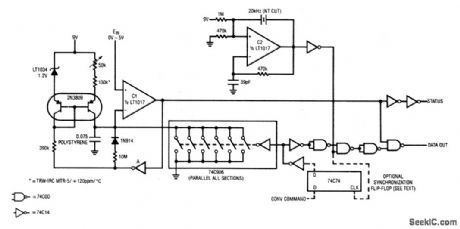

Basic Circuit

Low_power_10_bit_A_D_converter_1

Published:2009/7/22 22:31:00 Author:Jessie | From:SeekIC

This circuit is similar to that of Fig. 6-6, except that no external clock is required and typical quiescent power consumption is about 100 μA. Also, the additional ±1 LSB uncertainty of the Fig. 6-6 circuit is eliminated when the flip-flop shown in dashed lines is used. To calibrate, adjust the 50-kΩ pot for 1024 counts with 5.000 V at the input.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/Low_power_10_bit_A_D_converter_1.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: