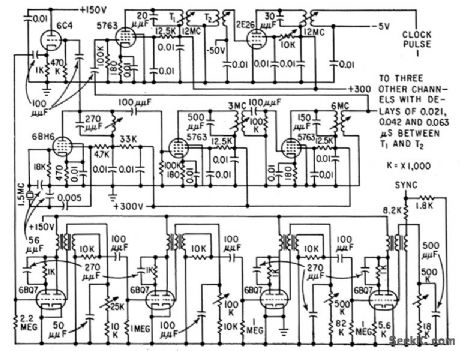

Basic Circuit

FOUR_PHASE_12_MC_CLOCK

Published:2009/7/11 2:48:00 Author:May | From:SeekIC

To minimize litter of synchronizing signals, fundomentcd frequency is chosen at one-eighth of dock rate or 1.5 Mc. Oscillator output is fed through two doubler stages and split into three channels, each having additional doubler followed by power amplifier, to provide low output impedance at any reasonable power level.-G.O. Olson, Design of High-Frequency Clock Pulse Generators, Electronics, 32:35, p56-57.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/FOUR_PHASE_12_MC_CLOCK.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: