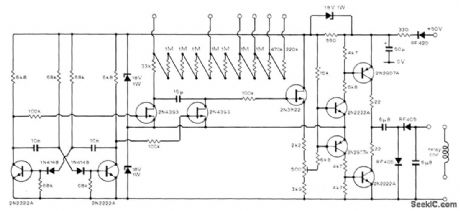

Basic Circuit

FAlL_SAFE_TIMER_FOR_TRAlNS

Published:2009/7/12 23:12:00 Author:May | From:SeekIC

Provides delays up to 4 min, adiustable in 2-s steps, with accuracy better than 5%. Patented circuit was developed by ML Engineering to provide appropriate automatic braking or other action if engineer on train fails to respond to signal within period of delay.-W.E. Anderton,Computers,Communication and High Speed Railways,Wireless World, Aug,1975,p 348-353.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/FAlL_SAFE_TIMER_FOR_TRAlNS.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: