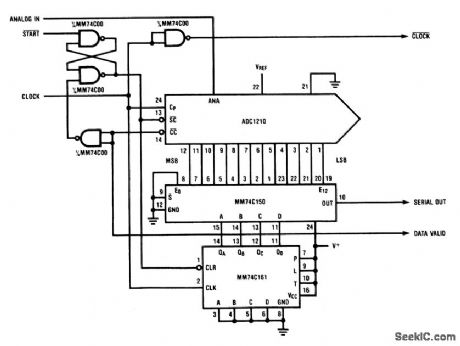

Basic Circuit

CMOS_A_D_converter_with_serial_output

Published:2009/7/22 22:56:00 Author:Jessie | From:SeekIC

In this circuit, 12 bits of data are shifted out serially using an MM74C150. This permits valid data to be available at the serial output port as fast as half a clock cycle after the most current decision. The data bits are synchronized to the falling edge of the system clock.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/CMOS_A_D_converter_with_serial_output.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: