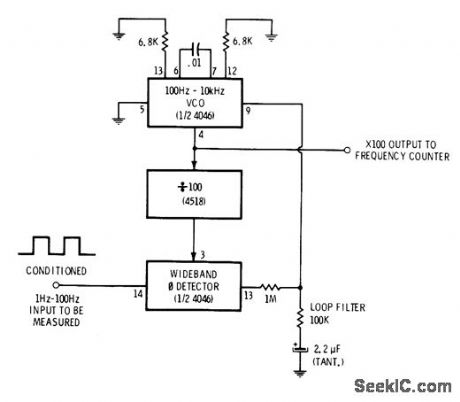

Basic Circuit

AF_MULTIPLIER

Published:2009/7/5 20:11:00 Author:May | From:SeekIC

Multiplies 1-100 Hz input signal by 100 to permit measuring frequency with ordinary counter. Half of 4046 PLL is connected as 100-10,000 Hz VCO whose output is divided by 100 in 4518 dual divide-by-10 counter for comparison with input signal in other half of PLL connected as wideband phase detector.Output of detector goes to loop filter and to VCO for locking VCO at 100 times input frequency.-D. Lancaster, CMOS Cookbook, Howard W. Sams, Indianapolis, IN, 1977, p 364-366.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/AF_MULTIPLIER.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: