Basic Circuit

7000_7999_MHz_PLL

Published:2009/7/5 22:37:00 Author:May | From:SeekIC

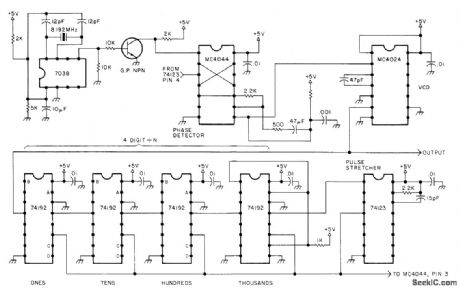

Provides output in 1-kHz steps under digital programming, except that first digit is hard-wired to 7 and does not change. VCO is Motorola MC4024, which generates square-wave output. For sineoutput, use low-pass filter at output of VCO to eliminate all frequencies above 7.999 MHz, or use different VCO. 74123 mono lengthens reset pulse generated by divide-by-N circuit. Terminals A, B, C, and D of 74192s go to grounding switches that are set to give desired division ratio, Article gives theory of PLL synthesizers YourseH!,73 Magazil,Oct,1977,p 182-188.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/7000_7999_MHz_PLL.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: