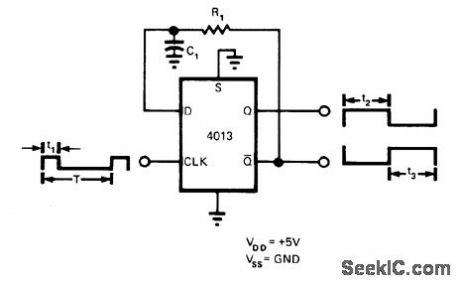

Basic Circuit

1_Hz_LAMP_BLINKER

Published:2009/7/5 22:53:00 Author:May | From:SeekIC

Single CMOS flip-flop generates approximately constant low-frequency signal from variable high-frequency signal. RC network in feedback loop determines output frequency, which is independent of rate at which flip-flop is clocked if output frequency is lowerthan dock frequency. If clock frequency is lower, output transitions occur at half of clock frequency. Provides two outputs, approxi-mately equal in duty cycle but opposite in phase. Circuit was developed to blink lamp at 1 Hz to indicate presence of active digital signal having variable duty cycle in range of 100 to 3000 Hz.-V. L. Schuck, Generate a Constant Frequency Cheaply, EDN Magazine, Aug, 20, 1975,p 80 and 82.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/1_Hz_LAMP_BLINKER.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: